PHY——内部接口协议【转发】

2017-07-27 by:CAE仿真在线 来源:互联网

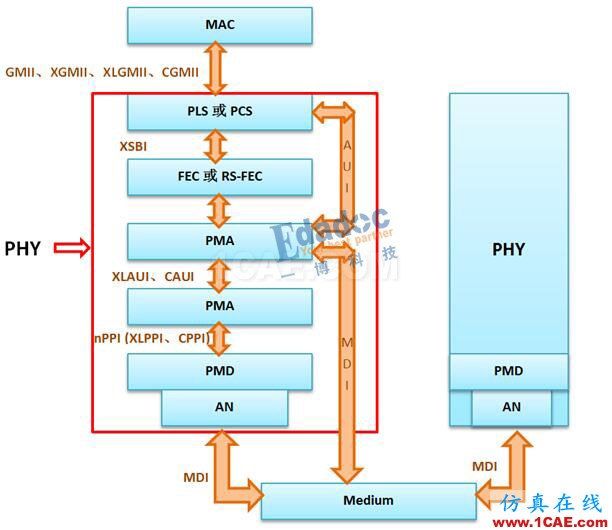

上周我们把MAC到PHY、PHY到PHY这两个子层之间的通信框架拎出来,把它们放在一个框图下,如下图所示:

图1 MAC与PHY框架

今天来讲讲这个PHY的内部、及其内部各个模块间的接口协议。PHY它包含了多个功能模块,功能模块的多少会因需要的不同而有所增减,比如:

只有10GBase-R、40GBase-R、100GBase-R的PCS需要FEC;

40GBase-R的PCS需要2个PMA、100GBase-R的PCS需要3个PMA;

只有≥1Gbps以上的背板应用场景才会用到AN。

1功能模块介绍

我们知道PHY在OSI(开放式系统互连)参考模型下,属于物理层,PHY由多个模块组成,各个功能模块的作用如下:

-

PLS:PhysicalSublayer Signaling,对MAC给的信息进行传递,只在1Mb/s、10Mb/s的应用场景才出现;

-

PCS:Physical Coding Sublayer,对MAC给的信息进行编码,应用于≥100 Mb/s的应用场景,比如完成8B/10B、64B/66B、256B/257B编码;

-

FEC:Forward Error Correction,前向纠错,与10GBase-R、40GBase-R的PCS 搭配;

-

RS-FEC:Reed-Solomon前向纠错,比单纯的FEC纠错能力更强,与100GBase-R的PCS 搭配,采用256B/257B编码;

-

PMA:Physical Medium Attachment,

-

PMD:Physical Medium Dependent,

-

AN: Auto-Negotiation Function,自动协商,使背板两侧的Device能够互换信息以发挥出彼此最大的优势;

2

模块间的接口

-

PLS与PMA间的接口,称之为AUI(Attachment Unit Interface);

-

PCS与FEC间的接口,称之为XSBI:10Gigabit Sixteen Bit Interface;

-

PMA与PMA间的接口,可以是chip to chip,也可以是chip to module,有两种:

XLAUI:40 Gigabit Attachment Unit Interface,4条lane,每条lane的数率是10.3125Gbps;

CAUI:100 Gigabit Attachment Unit Interface,10条lane,每条lane的数率是10.31250Gbps;

-

PMA与PMD间的接口,称之为nPPI(Parallel Physcial Interface)。

nPPI特定出现在PMD所接的媒介是光纤的情况下,比如40GBase-SR4、100GBase-SR10、40GBase-LR4协议。也就是说这种情况下的PMD是光模块,nPPI就必然是一种chip to module间的接口,这也是IEEE802.3标准与OIF_CEI标准兼容的地方之一。nPPI按照通道数量的不同分成两种。

-

XLPPI:40 Gigabit Parallel Physcial Interface,4条lane,每条lane的数率是10.3125Gbps;

-

CPPI:100Gigabit Parallel Physcial Interface,10条lane,每条lane的数率是10.3125Gbps;

3

接口协议对通

我们了解了这么多PHY内部的接口,对于很多人,最关心的还是产品设计该怎么做?不同接口的通道(channel)衰减多少能满足要求?下面就用简单粗暴地方式来一一列举,都是干货啊!开始划重点了!

1) PLS与PMA间的AUI接口

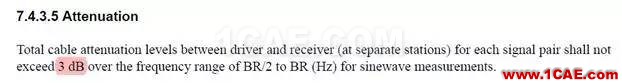

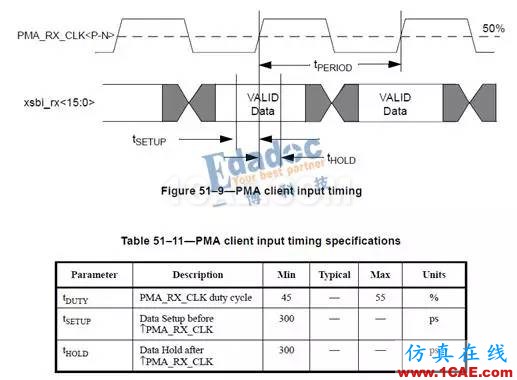

2) PCS与FEC间的XSBI接口

对通道没有给出无源的要求,但对接收端的信号质量和时序有要求,测试工程师应该喜欢这张标准定义方式。

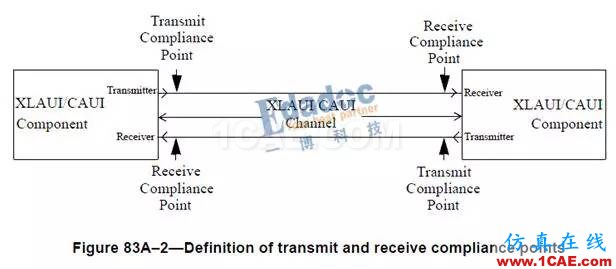

3) PMA与PMA间的XLAUI、 CAUI接口

-

如果是用于chip to chip的场景,则对channel的要求如下所示:

-

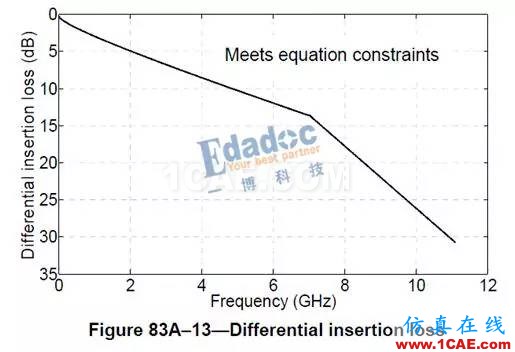

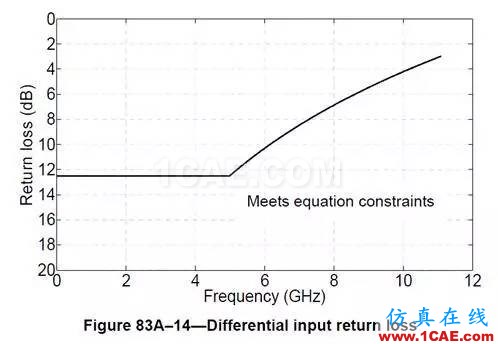

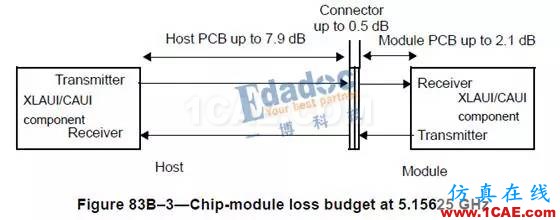

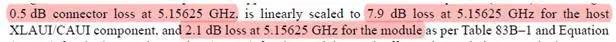

如果是用于chip to module的场景,则channel分为host、connector、module三部分,如下图所示:

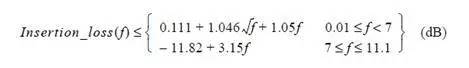

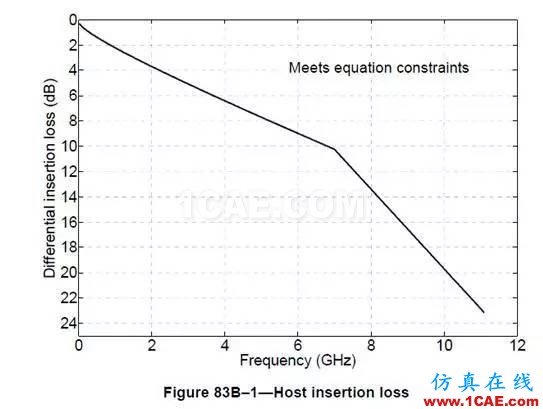

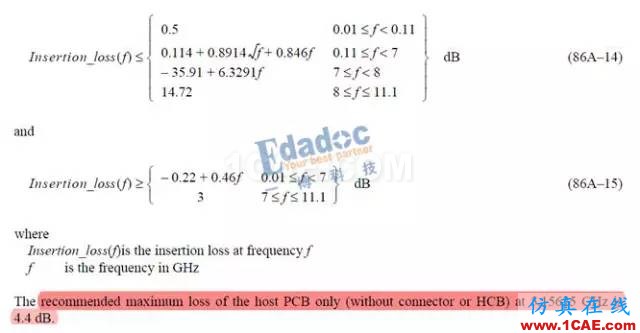

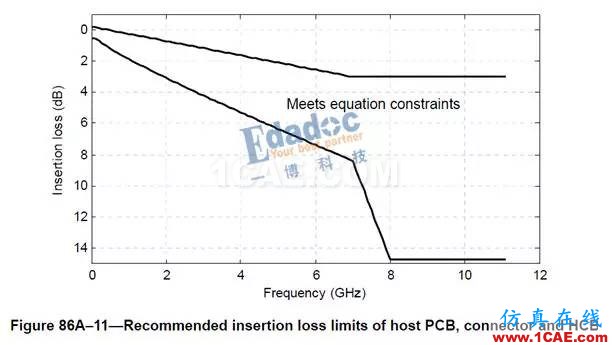

下面是对host插损的详细要求:

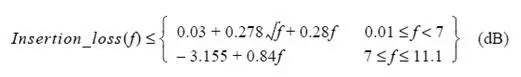

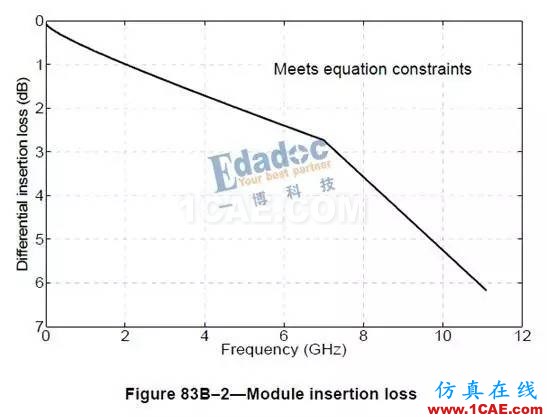

下面是对Module插损的详细要求:

4) PMA与PMD间的nPPI(XLPPI、CPPI) 接口

下面是对host部分的详细要求:

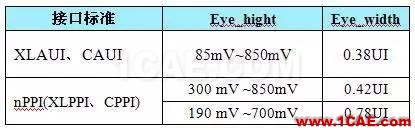

用插损、回损的表达方式对通道做要求,一部分工程师对于此感觉依然是云里雾里,看着这些所谓的dB完全不理解,那么下面还一种更为大家熟悉的方式:眼图,这也是在产品测试阶段最直观的标准。对于XLAUI、CAUI、nPPI接口眼图标准如下所示:

PHY子层内部接口今天就介绍到此,下周我们开始讲讲两个PHY之间的传输协议,通过背板、光纤传输的10G、25G信号有什么要求,比如10GBase-KR、100GBase-KR4等协议。

MAC需与其上层沟通,还需与其下层PHY沟通,其中MAC与上层沟通会完成以下两个任务:

问题来了

大家对今天讲到的PHY内部接口,在设计时有什么疑问、心得、好的经验?

本文转自公众号高速先生 刘丽娟 | 文

相关标签搜索:PHY——内部接口协议【转发】 EDA培训 EDA分析在线视频教程 Cadence Allegro PSPICE OrCAD PCAD Protel Mentor Graphics Synopsys培训课程 Fluent、CFX流体分析 HFSS电磁分析