升级到Allegro17.2-2016的10大理由之4:行业领先的背钻能力

2017-10-12 by:CAE仿真在线 来源:互联网

电子设计自动化领域领先的供应商 Cadence,与诸位分享Cadence Allegro、Sigrity等产品最新的科技成果和进展,并向电子设计工程师展示Cadence独有的PCB和封装设计解决方案。“升级到Allegro17.2-2016的10大理由”系列继续推出,欢迎共同探讨~~今天带来的是“升级到Allegro 17.2-2016的10大理由之4:行业领先的背钻能力”。

背钻的发展历程

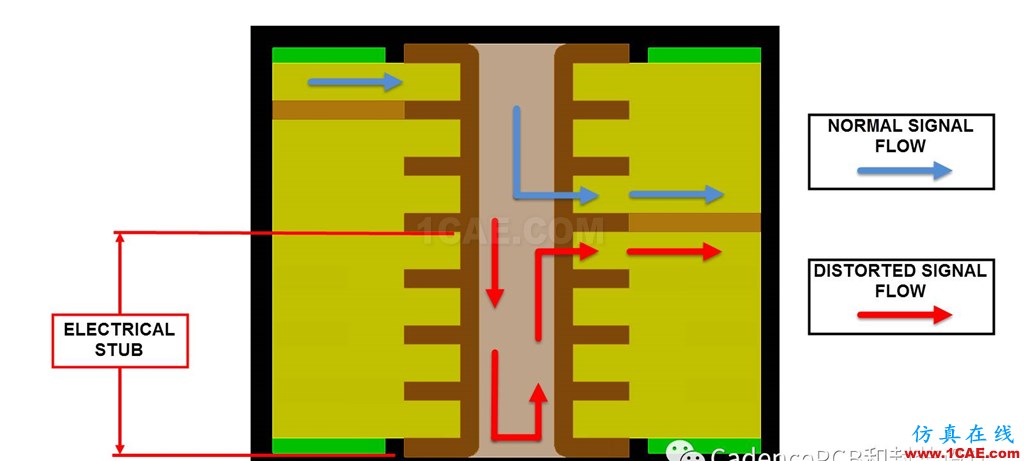

15年来,在很多电子设计中处理5Gbps或更高频率的高速接口布线已越来越常见。在信号过孔上存在Stub的情况下,高速信号换层将会对信号完整性产生巨大影响。总的来说,这些短截线会造成阻抗不连续和信号反射,严重影响有效数据传输速率的提升。

如何消除电子短截线?

-

使用一种称之为背钻的制板工艺,有时也被称为控制深度过孔。

-

做好规化和控制,保证高速信号走在特定的布线层,以此来减小Stub的影响。

-

用盲埋孔和微孔技术来布高速信号,这种方案可以解决一些局限和担忧,但会增加制造成本,而且压接连接器的管脚仍需用背钻技术来消除Stub。

早些年,制造商会根据关键网络列表,识别使用背钻的地方并做适当的调整。

在设计中引入背钻过程,有时对管理来说是个噩梦,需要与制造商更紧密合作。制造商会移除尽可能多的指定高速信号的短截线,根据增加的背钻尺寸调整每个背钻位置的特性、验证铜间距,来维持设计完整性。

为了让设计数据传递更顺畅,在Allegro15.7中,早已为简化制造端的数据处理打下了稳固的基石。

作为曾经的客户,2005年底,我曾是Allegro®PCB Designer 15.7 Beta测试团队的一员。我很高兴见证/测试了Allegro新的背钻解决方案。通过允许设计人员标识需背钻的网络,基于器件和引脚的属性分析并识别背钻位置等功能,使Allegro更上一层楼。需背钻的位置包含在背钻报告中,标有特殊的背钻符号,生成用于生产的NCDrill文件。即使有了这些提升,但仍然存在人为确保一致性的步骤(支持背钻位置有多种焊盘,手动设置背钻禁止区,允许制造商调整背钻尺寸)。

随着时间的推移,可以清楚地认识到未来的增强将会改进这个流程,会提供分析设计并且调整背钻位置特性的功能,同时生成完整的制造数据包来实现流水化制造。

Cadence与制造商和客户合作,调整了现有的解决方案,除了制造商移除大部分后处理步骤,还增强了几个区域的工具来支持背钻流程。作为一位产品工程师,我能够根据我自己之前作为客户的经历、并搜集客户们的反馈来调整这些功能。

-

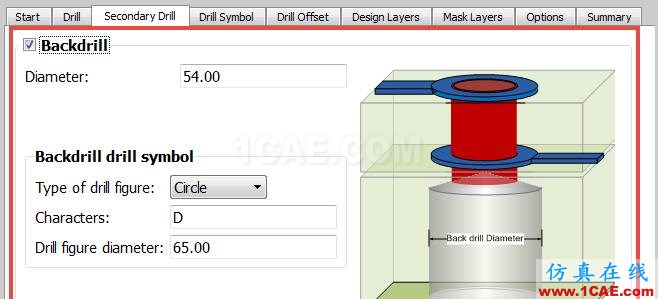

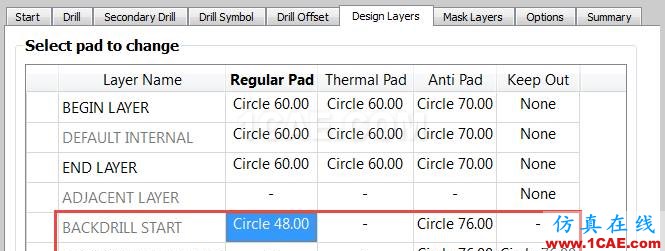

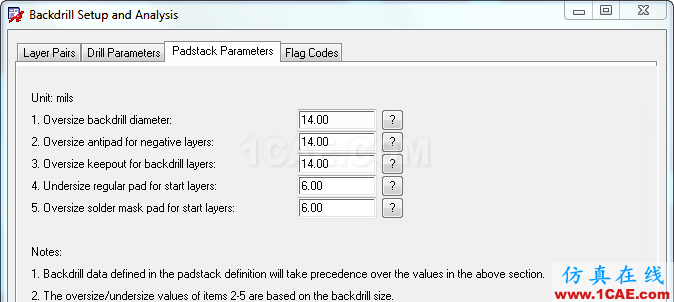

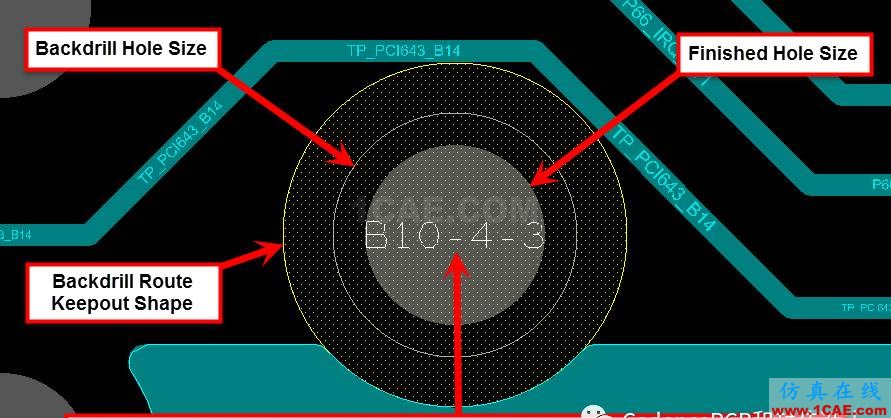

封装库中的焊盘支持背钻定义

-

有特定标识的背钻尺寸

-

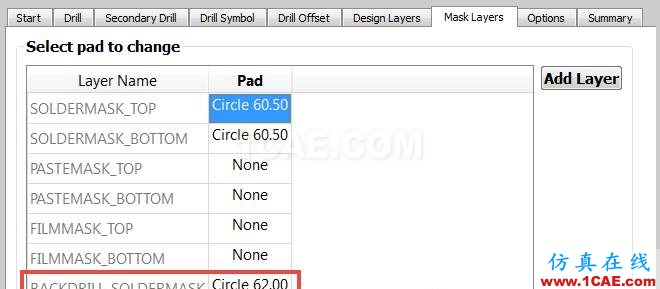

增强背钻焊盘进入和焊接掩膜

-

增加层禁区/间距

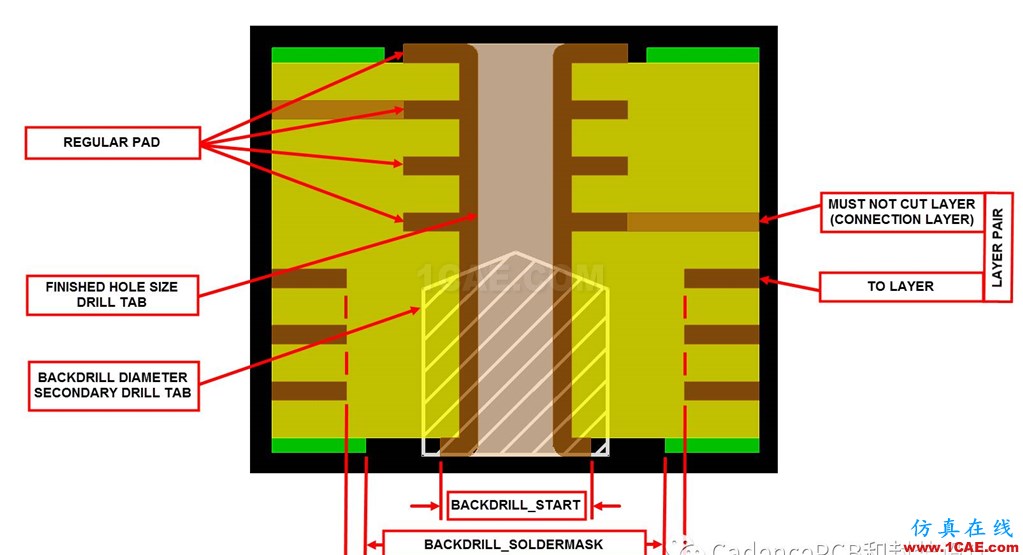

典型的背钻位置

-

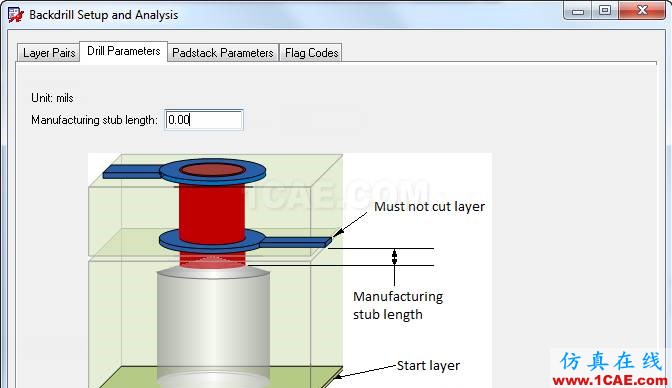

制造Stub长度-背钻后保留Stub长度(高级配置)

-

从不可切割层向下测量的剩余制造短截线长度,其表示电介质目标背钻深度

-

基于参数的设计层焊盘更新建成了背钻分析

-

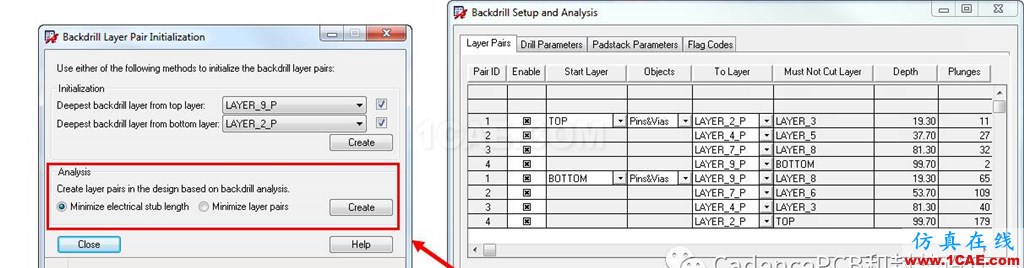

基于设计分析的改进模型可以快速定义/检查背钻层对规则

-

初始化:从顶层及底层的最深的背钻层

-

分析:最小化的电子短截线长度或最小化层对

-

带有特殊钻孔标识的背钻直径,用来说明背钻方向和深度

-

基于焊盘定义的间距自动生成走线禁布区

-

在背钻位置不再需要创建特殊的焊盘或禁止区

-

Show element指令可以报告在背钻位置引脚/过孔的背钻数据

-

基于在焊盘定义的背钻数据,现在在钻孔图例和制造NCDrill文件中报告真实的背钻尺寸

-

不再需要制造商基于电镀通孔调整尺寸

-

Backdrill Legends现在报告不能切割层、深度和制造短截线信息

-

画出跨区域细节,现在报告背钻跨度

-

在背钻过程中识别全部的测试点

-

在背钻位置没有测试点或增加测试点之外的钻孔

提升后的背钻解决方案解决了所有的疑惑点,消除了由于引入背钻所带来的担心。不再增加制造商的一次性工程费用(NRE),不再增加关于引入不同过孔和叠加技术的成本。可以传递给制造商一个更完整的制造数据包,其中包含IPC-D-356和IPC-2581中的背钻数据信息,以及用于传达背钻意图的完整文档。

相关标签搜索:升级到Allegro17.2-2016的10大理由之4:行业领先的背钻能力 EDA培训 EDA分析在线视频教程 Cadence Allegro PSPICE OrCAD PCAD Protel Mentor Graphics Synopsys培训课程 Fluent、CFX流体分析 HFSS电磁分析