信号完整性:反射重解-先导集“反射”的心路历程

2021-10-13 by:CAE仿真在线 来源:互联网

文 | 陈德恒 一博科技高速先生团队队员 系列:反射

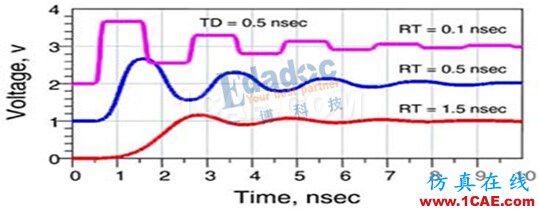

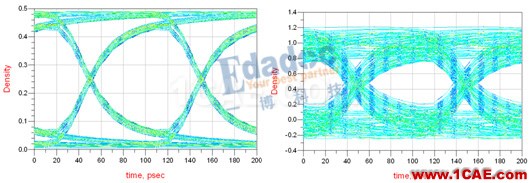

我们在介绍信号完整性的时候通常会说“当传输延时大于六分之一的信号的上升时间时,需要考虑信号完整性问题”,于是乎教科书里面都会配上一副类似于这样表现上升时间或者传输延时与反射的图片:

最开始的时候小陈说这段话时总会觉得很别扭,“我堂堂信号完整性怎么能是区区反射就能说明的呢?”之后随着理论与实践的深入,越来越觉得“反射中有黄金屋,反射中有颜如玉”,be the signal,弄清楚反射与串扰就拿到了解开信号完整性谜题的两把最关键的钥匙,小陈也很希望能陪各位书友将反射弄得更清楚一些,趁着围殴反射的机会,我们将反射系列修改补充后再复习一遍。

在先导集里,我们先来理一理信号这一路发展过来的心路历程。

在最初的时候,我们还是几百K几兆的信号,几十纳秒的上升时间。十几欧姆的驱动阻抗?没问题!小半米的走线?没问题!多负载乱七八糟的拓扑?没问题!

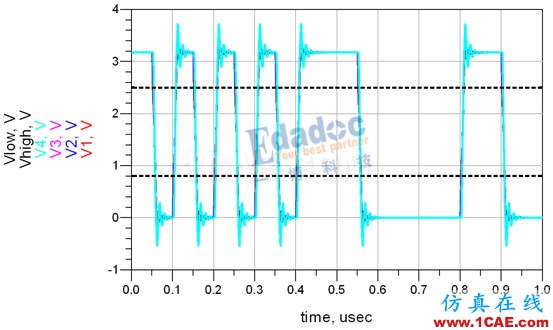

(10ns上升时间,4个负载,最长负载距离0.8m)

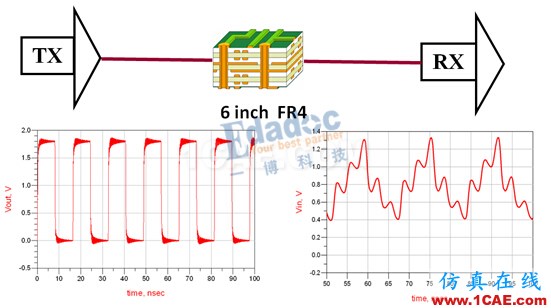

慢慢的芯片工艺越来越发达,一些时钟芯片,明明只有几十兆,但是上升时间却做到了纳秒以下,这时候一旦走线过长,原本好好的信号就会由于反射,即使是点对点的传输,一旦传输线过长,还是会使得接收端无法接收到正确的信号了。

这时候人们要考虑的是缩短走线的距离,或者在链路中间加一个redriver。

后来,出现了像DDRx这样的几百兆甚至上G的信号,驱动端的阻抗已经不是你想低就能低了,从十七欧姆到三十四欧姆,再不行的话还需要加匹配电阻或者拉低传输线阻抗来减小源端反射,甚至加上了ODT等等。拓扑也不是想怎么走就怎么走了,T点到远端树形,菊花链到fly-by,还要在末端疏通一下管道,加上上拉电阻。

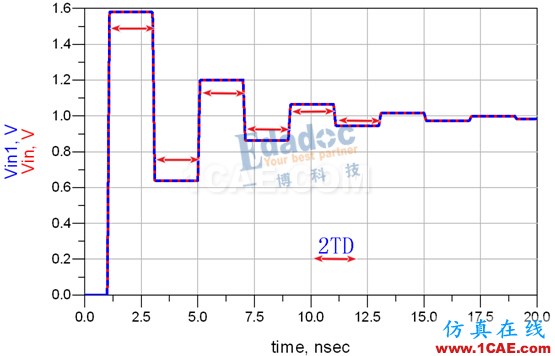

(点对点信号,上升时间100ps,驱动端阻抗为17与34欧姆的比较)

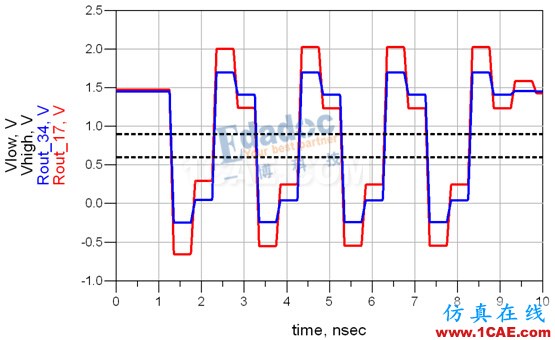

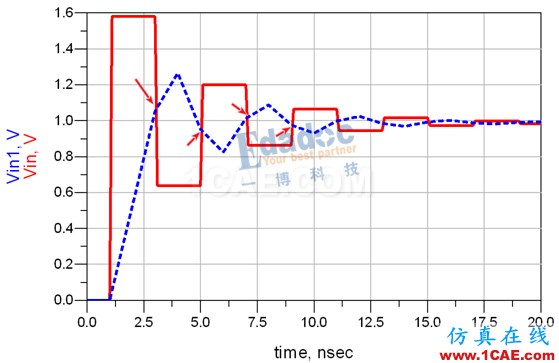

再后来,串行信号出现了,其目标是为了实现超高速传输。功耗大咱们可以降低电平;损耗大咱们可以用预加重均衡;串扰大咱们可以拉开间距;源端和末端这样的反射大的话•••那我们还是把发送端与接收端的阻抗都做成跟传输线一样吧:

(发送/接收端阻抗匹配与不匹配的对比)

现在的电子产品,从芯片的设计到系统的完成,都需要考虑反射的影响,好好的了解一下反射的原理对我们理解硬件设计有非常大的帮助。

Ps:特别提醒,在学习的过程中需要带入时间与长度的概念。

Ps:重发好没诚意,这里解释一下为何反射会淹没在上升时间内。

我们学习的时候公式是二维的,并没有增加时间的概念,于是源端低阻抗,末端高阻抗时,当发送端发送一个1V的阶跃信号时,我们通常看到的接收端波形是一幅这样的反弹图:

在这幅图中有两个关键的时间,一个是上升时间TR,一个是传输延时TD。什么是TR?是信号从0到1的时间,这是一定会需要时间的。上图中,信号的上升时间是100ps,传输延时是1ns。也就是说,第一个信号到达接收端的时候是1ns时,但是,信号达到最高幅值1.6V的时间是1.1ns。第二个反射波到达接收端的时候是3ns时。

当我们的上升时间变成了1ns时,我们经过反射之后的幅值能不能达到最高值1.6V?显然是可以的。我们的反弹图变成了这样,信号第一次到达最高幅值1.6V的时间是2ns。

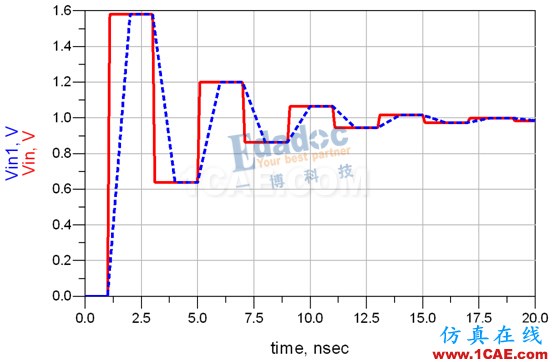

当我们信号的上升时间为2ns的时候呢?也是可以的。但是如果当信号的上升时间大于2ns时,接收端的信号还能达到1.6V吗?永远不行了,因为在3ns处,第二次的反射波已经过来了。于是,当信号的上升时间为3ns时,反弹图变成了这样子:

注意箭头位置,信号上升的斜率发生了明显的变化,这是因为多次反射波的叠加。

当信号的上升时间再长一点呢?他可能就不止会叠加第二次的反射波,还会叠加第三次第四次第五次第六次,多次的反射叠加之后,就几乎看不出来反射的现象了。

在后文中,会将信号分解,从另外一个角度去分析解释该现象。

相关标签搜索:信号完整性:反射重解-先导集“反射”的心路历程 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析