T29DesignCon译文:描述25+Gbps连接器特性的新方法

2016-09-22 by:CAE仿真在线 来源:互联网

摘要:

这篇文章呈现了几种描述连接器、过孔和印刷电路板特性的新的发现。指出减小信号之间的偏移可以提高整个通道的插入损耗对串扰的比率(ICR)。为了最优化25+ Gbps通道的性能,专门铺设了一块集成了高密度BGA连接器和两跟6英寸传输线的电路板,并且应用了编织特性非常平整的Megtron-6板材。应用了一种新的去嵌工具对两根6英寸传输线进行模型提取,这种工具可以通过优化使得时域和频域响应完全匹配。连接器参数通过一块大的电路板直接提取,并和3D仿真结果对比,过孔基于随频率变化的介电常数和浸锡效应来仿真。指出在需要更少的内存和CPU仿真时间的前提下,具有有效直径的平滑过孔可以得到相似的阻抗和时延参数。最后,通过相关数据说明了连接器,过孔以及PCB在仿真和测试结果中有极好的一致性。

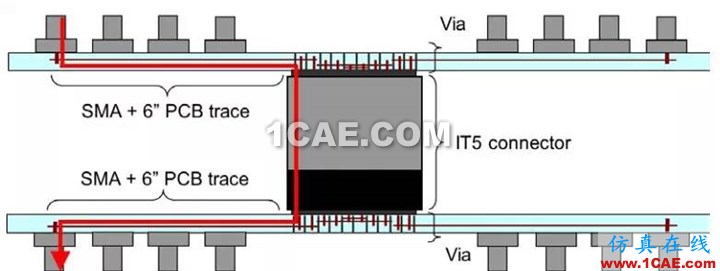

在芯片到芯片的连接通路中,连接器通常是最大的阻抗不连续点和串扰源。为了得到正确的连接器(IT5)参数,必须设计一个测试数据不会随着PCB的变化而失真的测试工具,仿真模型也必须和测试工具有相同的尺寸和PCB板材。为了从测试工具提取连接器和过孔的参数,还需要一个精确的去嵌工具。本文评估了PCB的结构以及它对整个通道的性能影响。介绍了几种可以很好的协同仿真和测试的新方法。

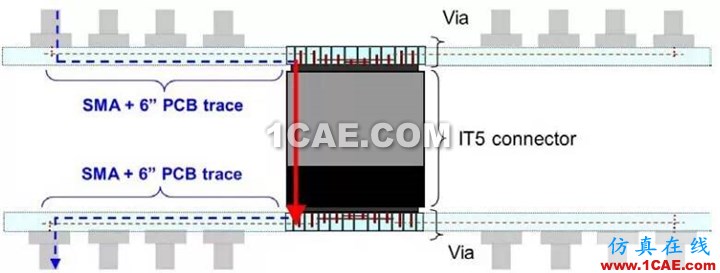

最初的测试工具主要凸显了高速连接器的性能,但是测试数据和仿真结果有很大的差异。用本文所介绍的方法设计了一个新的测试工具后,测试数据和仿真结果都有了很多的改善。如图1所示,每一个测试工具由一个主板和一个子卡通过一个IT5连接器连接起来。每一个测试工具可以提供超过15个差分对以供测试。

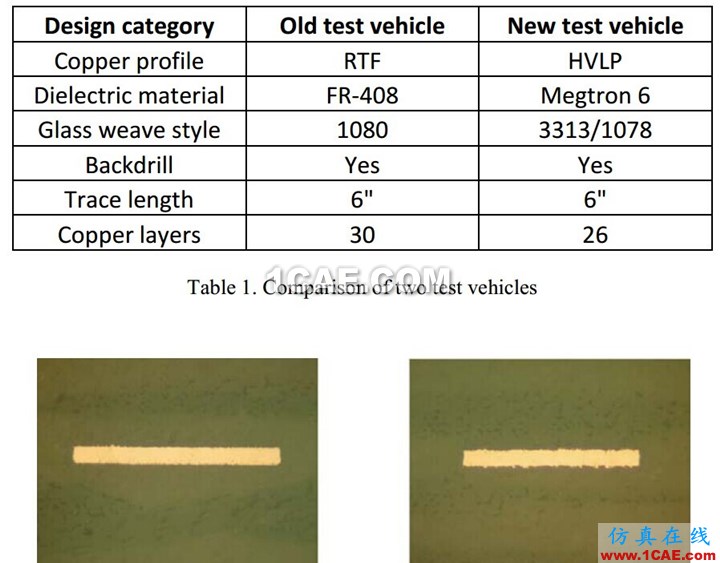

主板和子卡都提供了6英寸的差分带状线,并连接到SMA接口。第一块(旧的)PCB采用了FR408板材和RTF工艺,厚度为30层,第二块(新的)采用了Megtron6的板材和超低剖面(Hyper very low profile,HVLP)铜面处理,板层为26层。另外,为了验证介质材料和铜面效应,改变了玻璃纤维的种类来提高整个通道的性能。旧的PCB采用了常用的1080,新的PCB用了3313和2-ply 1078玻璃纤维来提高整体介质的一致性。

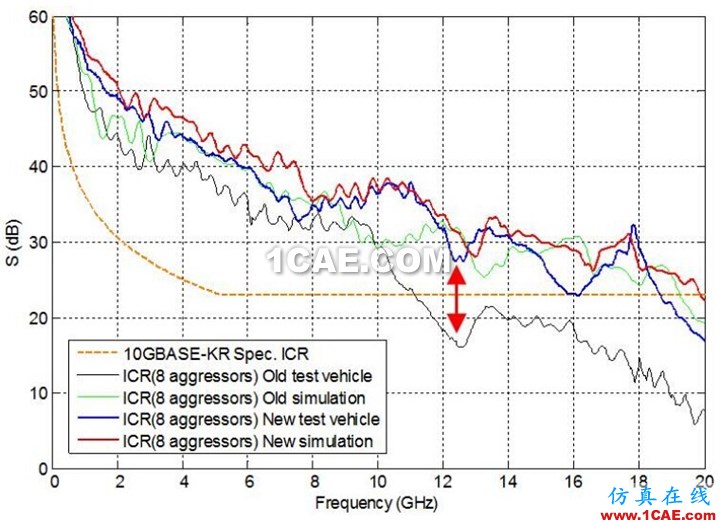

图2显示了基于两种测试工具对ICR的测试和仿真数据,ICR曲线是IEEE 802.3ap规范里面的定义,用来比较通道中信号的衰减和不需要的噪声。图2的ICR曲线包含了SMA接头、带状线、过孔以及连接器。基于旧的测试工具的仿真结果可以在19GHz之内PASS,但是测试数据只能在11GHz之内PASS。这么大的差别是由于PCB生产工艺和板材特性不够完美引起的。

基于新的PCB的仿真和测试数据吻合的很好,仿真模型也没有随着制程偏移有很大的变化。为了减少因为制程偏移而引起的通道衰减,必须在前期仔细的设计PCB。图2中对于新的PCB的测试结果有了很大的改善,这是因为应用了更好的PCB板材和PCB设计规范。本文后面的部分将来说明如何设计新的PCB以及如何应用新的去嵌工具和方法来验证结果。

B

PCB材料选择

在25+ Gbps通道设计中,PCB材料是一个非常重要的因素,它决定了整个通道的信号衰减和测试数据的完整性。低损耗介质加上平整的玻璃纤维可以很大程度的提高通道性能。有很多种不同的玻璃纤维和树脂可以选择,本文主要学习1080和1078两种编织效应以及对比其不同。

玻璃纤维编织效应对信号对之间偏移的影响

1080编织的纤维束紧紧缠绕,产生出比较大的环氧树脂束和玻璃编织。在图3所示的例子中,一对差分带状线中一根线在环氧树脂上面,另一根线在玻璃纤维上面。一般来说,环氧树脂的介电常数大约为3,但是玻璃纤维的介电常数根据生产工艺的不同,在5和6之间。不同的材料有不同的介电常数,所以在环氧树脂上面的传输线阻抗比较高,而在玻璃纤维上面的传输线阻抗比较低,而且传输延迟也和介电常数相关,这导致两条传输线的延时不一样,这将造成差分线之间产生偏移。这种偏移会很大程度的影响通道的插入损耗和串扰。

对于1078来说,玻璃纤维束伸展开来,平坦的分布在表面之上,PCB玻璃纤维之间的空隙减小,每一根传输线所对应的介电常数在很大程度上趋向一致,所以差分线之间的延时匹配,也可以使差分对之间的偏移最小化。

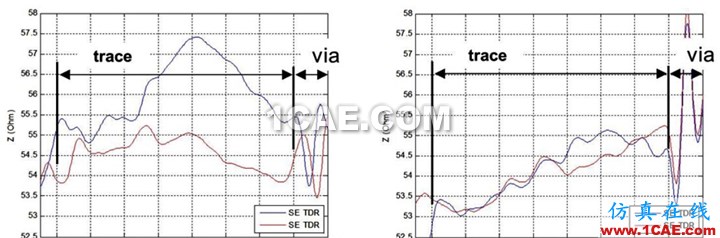

从时域角度也可以看出这种差异,如图4所示,在1080玻璃纤维编织的情况下,两根传输线的阻抗(20/80上升时间为50ps)有很大不同。阻抗高的传输线也会有更快的信号传输。从测试结果来看,两根单端线到达接口过孔处的时间不一样,引起差分对之间的偏移。而在1078玻璃纤维编织的情况下,两根单端线的阻抗非常接近,传输速度也一样,所以到达过孔的时间也相似。

线间偏移会导致差分对性能衰减。图5展示了一组差分对之间的偏移为~30ps时,差模插入损耗和远端串扰的恶化情况。可以看出,线间偏移被修正以后,差模插入损耗和远端串扰都有了非常明显的改善。为了整个通道达到好的性能和关联性,最小化线间偏移的影响,在设计PCB的过程中深入了解材料特性和制造知识非常重要。

导体损耗和介质损耗

为了保证25+ Gbps的通道性能,必须理解铜和介质材料的特性以及控制信号的衰减。现在市场上有很多不同种类的铜箔可供选择,有反面处理铜箔(RTF),超低轮廓铜箔(VLP)以及超级低轮廓铜箔(HVLP)。不同种类的铜箔有不同的导体损耗特性和不同的价格。如果信号衰减不能在PCB设计阶段精确的预测,通道实际的眼高和眼宽可能和仿真结果会有不同。PCB介质材料在介电常数和损耗特性上也有很大的差别,比如一般的FR408材料的损耗因子为0.015,而其他低损耗材料的损耗因子可能为0.005.

为了预测整个通道的全部损耗,必须要精确的计算导体损耗和介质损耗。IEEE网站提供了一份Excel表格,可以用于为802.3bj计算带状线的导体损耗和介质损耗。它提供了Megtron-6,FR408以及Nelco N4000-1三种材料,数据包含了到20GHz以内随频率变化的介电常数和损耗因子。只要用户输入传输线长度,介质层厚度和走线尺寸,工具就会技算出通道的损耗曲线。另外,还有三种铜箔粗糙度的选择:低,中,高。

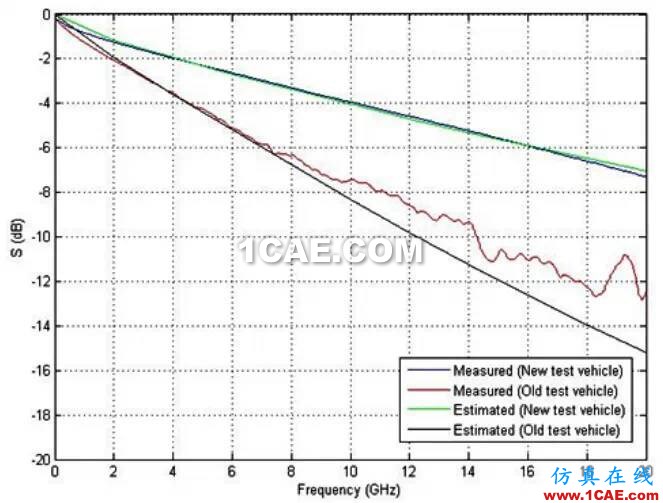

为了测试这个计算器的精确度,只测试了基于新旧两种测试夹具上面两对6英寸的带状线,表1给出了两种测试夹具的结构,图6显示了RTF和HVLP的横截面,图7为两种夹具的测试和预估的损耗结果,预估的结果是从上文提起的Excel计算器计算而得,其中RTF铜箔选用高粗糙度,HVLP铜箔选用低粗糙度。

E

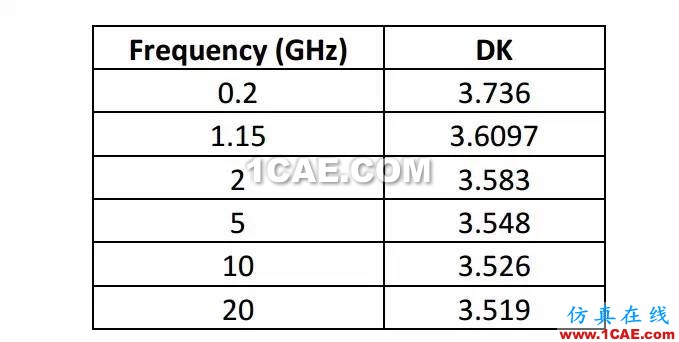

随频率变化的DK值提取

FR408和Megtron-6是常用的PCB材料,但是不是所有的PCB都会用这两种材料。另外,PCB玻璃纤维编织的种类也会改变材料的有效介电常数。下文描述的方法适用于带状线结构,可以有效提取任何材料的介电常数。为了得到可靠的数据,这种方法需要一个精确的去嵌工具,下面介绍一种可以精确去嵌的新工具。

In-Situ去嵌

In-Situ去嵌(ISD)是AtaiTec公司提供的新的去嵌程序,它可以移除测试夹具的影响(SMA接口和引线)和提取DUT的S参数。这个工具的主要功能如下:

ISD需要2x长度通过测试测试板,但是不需要和DUT板有相同的阻抗,这是因为ISD仅仅使用测试板做为频域和时域优化的参考,不是用来直接去嵌。

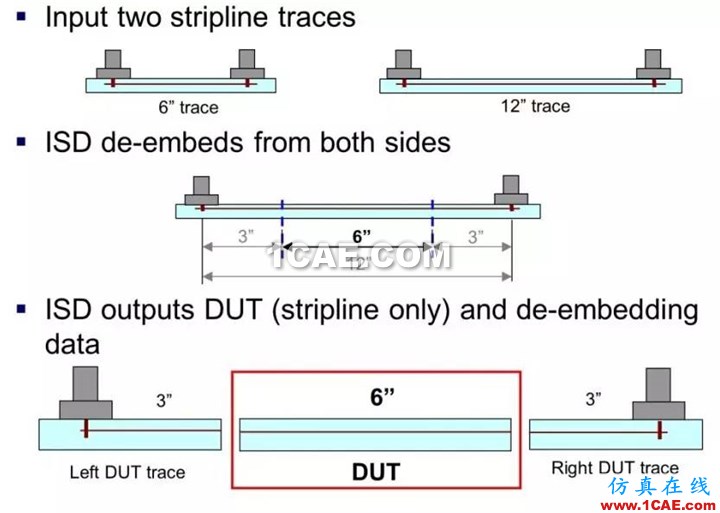

ISD仅需要2个参数:一个2x参考板的测试文件和一个从SMA到SMA DUT板的测试文件。用户只要输入这两个文件,ISD会自动去嵌SMA接口和连接引线的影响。ISD会输出三个S参数,左边去嵌文件,右边去嵌文件以及DUT本身。

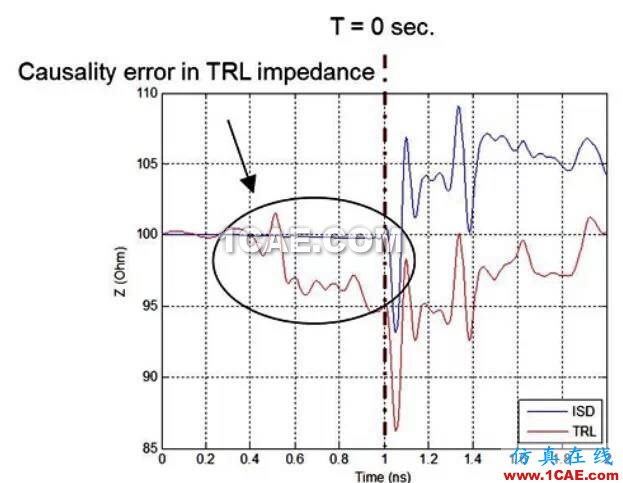

图8展示了一个例子,ISD之后的DUT阻抗是因果的,但是经过传统的TRL校准以后的阻抗确实非因果的。传统的方法会引起非因果问题,主要是因为校准和实际DUT的不同。

F

DK值提取

为了提取到精确的频率相关的介电常数,需要只对带状线测试,而这种测试允许存在由SMA接头和过孔带来的阻抗不连续。由于ISD移除了DUT板之外阻抗不连续的影响,剩下的DUT的结果就非常准确了。这个例子中,为了提取一对6英寸的带状线,在相同的PCB层上构建了一对6英寸的线和一对12英寸的线,其中6英寸的线主要是用来去嵌的。如图9所示,ISD会从每一个SMA接口开始去嵌,留下中间DUT的6英寸线。左边和右边的去嵌文件包含了SAM接口,SMA过孔和3英寸的带状线。

现在得到了6英寸带状线的测试数据,下一步需要计算带状线周边材料的介电常数。信号的传输速度可以在没有不连续的情况下根据相位延时很容易的得到,然后随频率变化的介电常数可以通过光速和信号传输速度的比值得到:

验证PCB结构

经过多年的发展,PCB的制造工艺已经非常精确,但是过孔和传输线的结构还是会有变化。为了保证仿真模型和实际结构一致,必须进行验证。

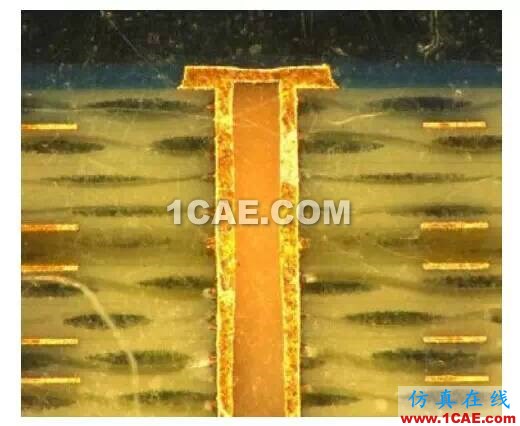

过孔的横截面

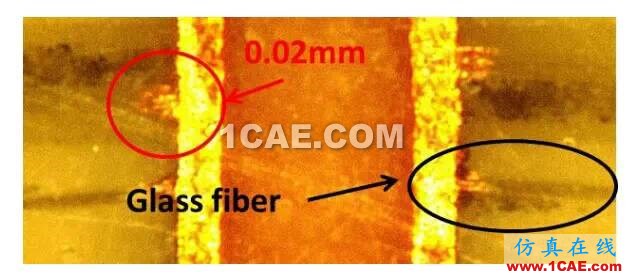

新的测试夹具生产以后,提取了一对差分线过孔的横截面(图10)。像Via直径、位置、Pad直径,铜箔移位以及介质厚度都经过了测试并且发现和仿真的数据有一点不同。

I

渗镀

渗镀是在过孔孔壁上有小的突出物存在,这些突出物看起来是附着在和孔壁相交的玻璃纤维上,当环氧树脂损坏或和玻璃纤维分开的时候,铜箔会和玻璃纤维一起移动,而环氧树脂会在钻孔或层压的工序中损坏。在新的测试夹具中,渗镀为20微米,IPC规范要求渗镀不能大于80微米。

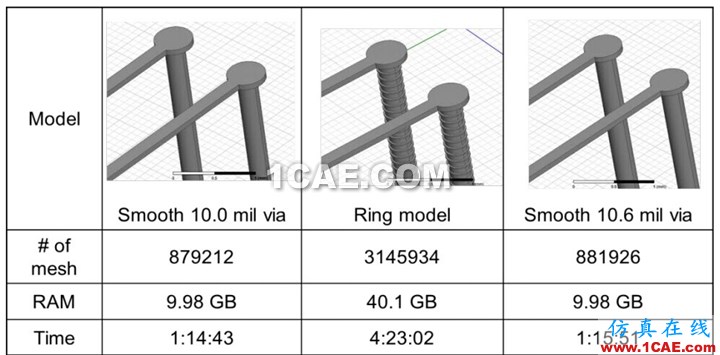

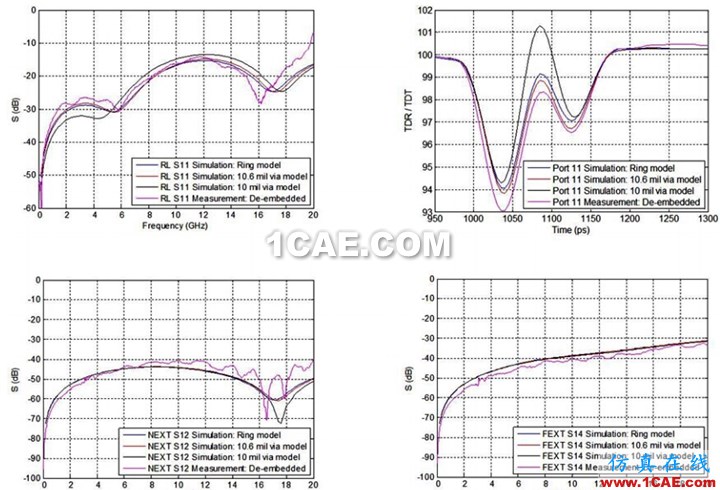

因为生产新的测试夹具是为了25+ Gbps的数据速率,所以渗镀对信号完整性的影响需要考虑。去嵌的测试数据包含了过孔和一条很短的线。创建了三种不同的仿真模型来观察渗镀的影响。最基本的情况是10mil的过孔,没有渗镀,第二个模型用100微米的同心圆使得有20微米在孔壁突出,来表示实际结构。最后一个模型是10.6 mils直径的平滑过孔,想要来观察没有同心圆的渗镀影响。表格3比较了用HFSS来仿真这些模型所用的内存和CPU时间。

图12显示了Ring model,10.6 mil模型和测试数据之间有很好的相关性。可以明显的看出来,为了精确和高效的仿真过孔,过孔的直径可以比实际情况大一点来表示渗镀的影响。

需要注意的是有和没有20微米的渗镀,在阻抗上会有大约2欧姆的差异(30ps上升时间的情况下)。如果PCB有80微米的渗镀,阻抗的差异会更大一点。

通道性能

对于25+ Gbps的通道,插入损耗和串扰的比值(ICR)是一个非常重要的测试项目。仿真和测试的ICR数据不仅需要在整个通道上一致,而且需要在连接器+过孔的数据上一致。很好的一致性说明整个仿真,设计以及参数提取方法在按照期望的方式进行。

整个通道的一致性

PCB传输线的模型是仿真和测试一致性中最大变量中的一个。任何模型都不能复制由玻璃纤维和制造工艺带来的随机影响。本文介绍了级联由仿真和ISD提取得到的连接器和过孔的新的方法,来完成对整个通道的一致性。

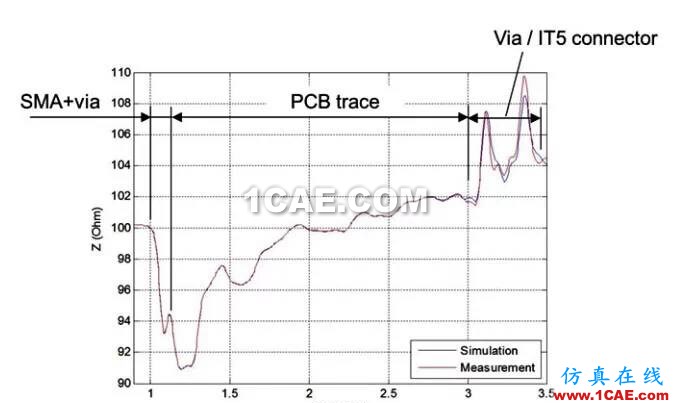

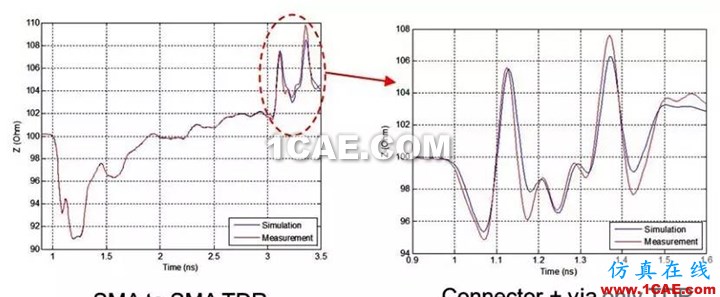

图14比较了对于整个通道测试和仿真的差分阻抗,其中仿真模型由ISD提取的SMA+Trace模型和HFSS仿真的IT5连接器+过孔模型级联而来。从图14可以清楚的看到由ISD提取的PCB阻抗有很大的变动性。测试和仿真仅有的区别是在IT5连接器+Via区域。

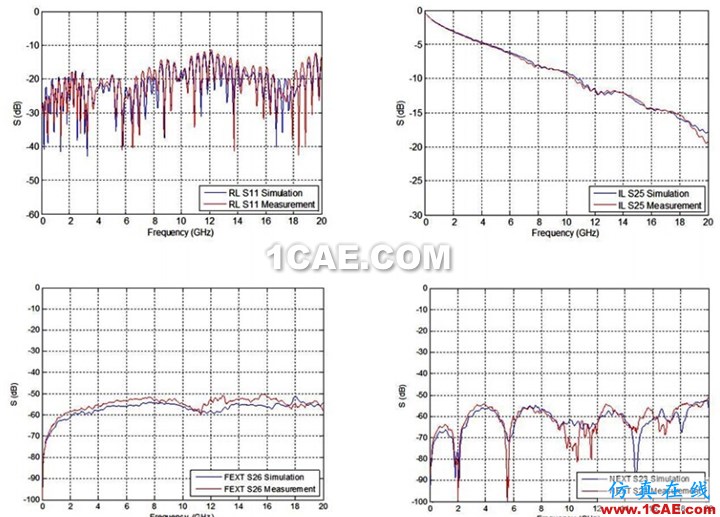

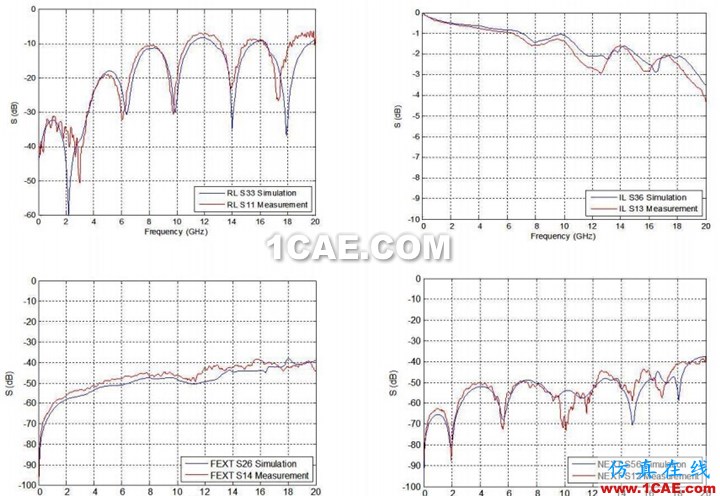

图15说明测试和仿真在各个参数中都由很好的一致性,插入损耗(IL),反射损耗(RL),近端串扰(NEXT)以及远端串扰(FEXT)。

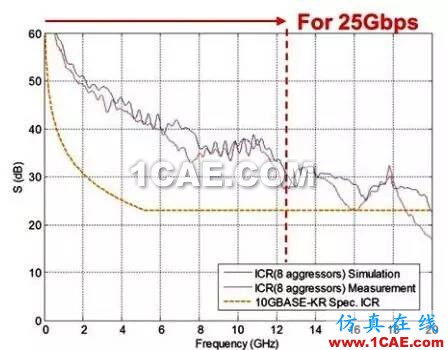

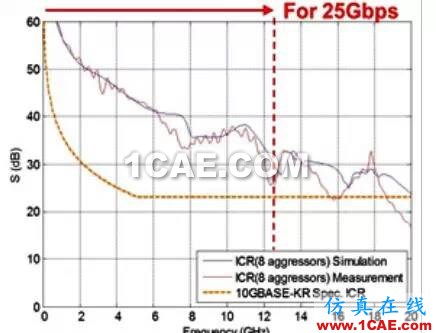

图16也说明了仿真和测试在ICR参数上也有很好的一致性,它再次确认了整个系统对于25+ Gbps信号的性能。

连接器和过孔的参数描述

连接器和过孔通常是系统通道中最大的阻抗不连续点和串扰源。为了理解通道的性能瓶颈,就需要理解连接器和过孔在实际的通道中的性能。本文说明了在PCB设计中影响通道性能的主要因素,并且通过一个很大的演示板来描述连接器和过孔的参数。一块比较大的演示板很容易通过实际操作来说明器件的性能。而通过演示板来提取DUT的参数可以帮忙我们确认导致仿真和测试不一致的原因。

图18展示了整个通道以及去嵌之后连接器和过孔的阻抗波形。因为有更多的高频信号保留,去嵌之后可以看到更多细节。去嵌掉SMA和PCB 走线之后,DUT(IT5连接器+Via)在仿真和测试之间有很好的一致性。

图19展示了IT5连接器+过孔的IL,RL,NEXT,FEXT。仿真和测试之间的一致性保持的非常好,尤其是在DUT是从一个很大的电路板上提取而来的条件下。

图20又一次展示了仿真和测试在ICR项目上的一致性。注意ICR在整个通道(图16)和只有连接器+过孔(图20)的相似性,可以理解这个例子中大部分串扰来自连接器和过孔,而ICR的变化很小。

结论

这篇文章讨论了下面几个主题:

•玻璃纤维以及其对信号偏移的影响

•信号偏移对插入损耗和串扰的影响

•渗镀以及其对阻抗的影响

•用ISD提取DUT的参数

•提取带状线参数并计算随频率变化的DK值

•为了整个通道一致性,提取SMA和走线参数

为了论证IT5 连接器在25+ Gbps信号通道中的性能,制作了两种测试夹具。新的测试夹具应用了更好的材料和设计方法,也有了更好的性能。用ISD的方法来精确提取传输线模型,对于整个通道和只有连接器+过孔的结构中,TDR,S参数和ICR都有很好的一致性。

中文文档下载链接:

http://www.hwthinktank.com/Uploadfile/file/20150504/描述25+%20Gbps%20连接器特性的新方法_高速总线_20150504.pdf

英文文档下载链接:

http://www.hwthinktank.com/Uploadfile/file/20150504/New%20Methodology%20For%2025_Gbps_HS_20150504.pdf

原文作者:

Adam Nagao, Hirose Electric

Toshiyuki Takada, Hirose Electric

Ching-Chao Huang, AtaiTec Corp.

Jeremy Buan, Hirose Electric

Kunia Aihara, Hirose Electric

Phillip Li, Cisco Systems

Atsushi Mihara, Yamamoto Mfg

中文译者:

王彦武

相关标签搜索:T29DesignCon译文:描述25+Gbps连接器特性的新方法 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析