信号完整性SI(SignalIntergrity)概述之一高速串行信号的仿真

2016-10-12 by:CAE仿真在线 来源:互联网

随着系统速率的逐年提升,高速数字信号的速率越来越高,信号完整性SI(Signal Integrity)越来越受到关注。信号完整性(Signal Integrity)简称SI,是指在信号线上的信号质量,数字信号质量差,不是由某一单一的因素导致的,而是PCB设计中多种共同的因素共同引起的,如器件选型,PCB板阻抗,损耗控制,模数混合设计等,主要表现的信号完整性问题包括反射,串扰,地弹,振铃等。

特别是兴森科技有些客户经常反馈的,较大的过冲,振铃,加上系统较小的噪声裕量,给系统时钟带来了非单调性,造成系统的误判,这是令所有硬件开发人员头疼的事情,有时候即使通过高速实验室调试,测试的方法找到了问题的原因,但是PCB已经成型,不得不再次花大把的时间跟金钱重新打板,贴装,调试,据兴森科技现有设计类客户统计平均改板次数为1.2次。

所以通过在研发阶段借助目前的EDA仿真工具,将SI问题定位在设计的前端尤为重要。客户的问题就是兴森科技的问题,在这里将分期为大家介绍高速系统中的信号完整性问题。

(1)高速串行信号完整性分析

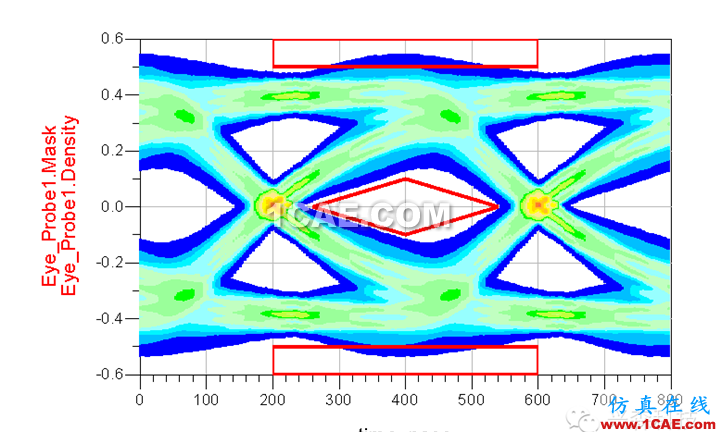

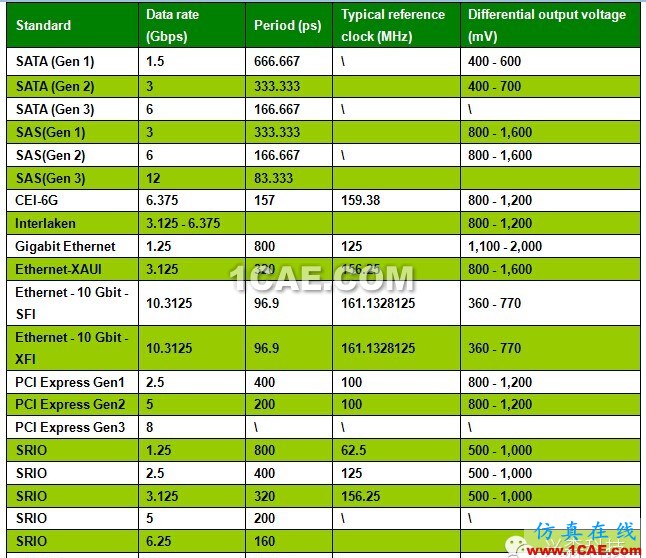

常见的高速信号如PCIE,SATA,GTX,GTP,SRIO,USB3.0,XFP,SFP,XAUI等,评估整条链路上信号从发射端到接收端的表现情况,通过频域上(如S参数)和时域上(如信号波形,眼图)的仿真评估,来确保信号的有效传输。

图一:常见的串行背板

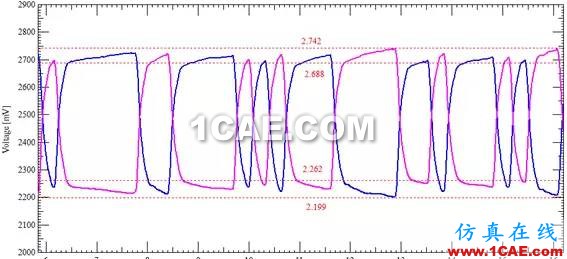

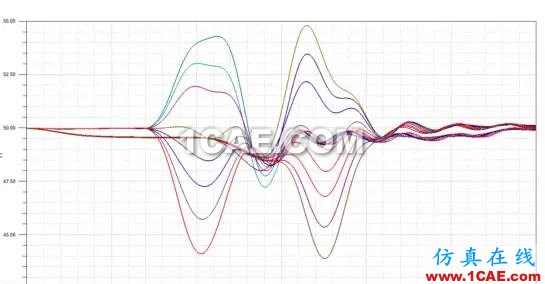

图二:高速信号波形图

表一:常见的高速信号列表

(2)高速背板信号完整性分析

通过背板的仿真,可以有效地解决高速信号经过较长背板后由于衰减及反射等信号完整性问题而引起的信号不能有效地进行传输的问题,背板的仿真可以指导客户选择适当的背板材料,并对高速连接器进行优化,有效的降低研发成本,减短设计周期。

图四:不同层信号的损耗

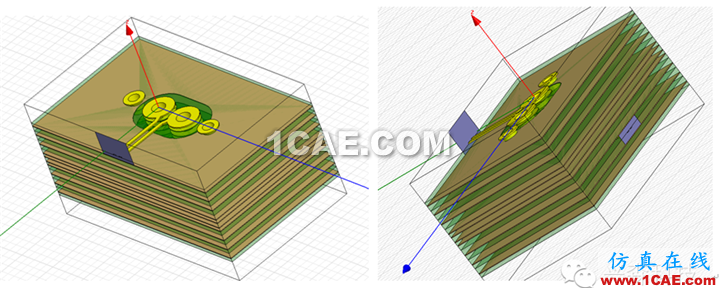

(3)过孔优化

对于PCB上高速的换层过孔和连接器过孔,通过3D软件建模分析,有效地控制过孔阻抗,给出过孔的最优尺寸,从而优化信号质量,提高设计成功率。

图五: 过孔3D模型

图六:不同反焊盘对过孔阻抗的影响

综上所述:

整个高速串行通道中,PCB设计的线宽线距,过孔的物理结构,走线的层次选择,是否背钻(back drill)都会影响到高速数字信号的传输,都需要前期仿真介入,做到科学设计,无忧无虑。

相关标签搜索:信号完整性SI(SignalIntergrity)概述之一高速串行信号的仿真 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析