DDR3 里 REF CA 和VDD之间接电容,有何作用?/PCB上定位孔,如何接地?

2016-11-07 by:CAE仿真在线 来源:互联网

本文转载自:微信群"SI-list 中国【2】"聊天记录如下:

作者:邵鹏、Sandy、vivianwu 、联想win 、Nevdia刘旭升、乔健、荆棘鸟、李黎明、沈云峰、joy

Sandy 下午3:46

请教个问题

Sandy 下午3:46

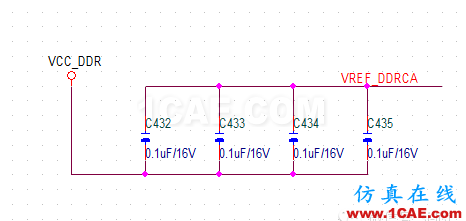

DDR3 里 REF CA 和VDD之间接电容,有什么用?麻烦大家了

Sandy 下午3:46

win 下午3:50

@Sandy PCB设计 这个不用吧,这个电压不是ddr电压分压得到吗

Sandy 下午3:53

@win 是分压得到的,但通过电容接VDD这个电路也有,我还对比了Jedec上的公版,也有这些电容

vivianwu 下午3:54

vref_ddrca : addresss/ctrl/cmd reference voltage

vivianwu 下午3:55

jedec sch 也有畫出來

Sandy 下午3:55

嗯,不理解是啥作用

vivianwu 下午3:56

vref_ddrca : addresss/ctrl/cmd reference voltage

Sandy 下午3:56

vref_ddrca 通过电容接VDD是啥作用

黄跃辉 下午3:57

是有点奇怪,如果是滤波为什么不直接接地呢

vivianwu 下午3:57

vref_ddrca 通过电容接VDD是啥作用 這要問專業的 我不是 [流泪]

win 下午3:58

我们没接,好像没发现什么问题

Sandy 下午3:58

嗯,Memory Down 的图才能看到,接DDR插槽的看不到这个电路

PCB-Kevin 下午3:59

哪位有Intel芯片代理商的联系方式?求。。。

win 下午3:59

我们不是做memory的

李yongyao 下午4:03

跨接几个电容,能保证ref跟随住vdd

vivianwu 下午4:03

[强]

黄跃辉 下午4:04

酱紫

Sandy 下午4:04

为什么 ref DQ 就没有

李yongyao 下午4:06

@Sandy PCB设计 这个问题很好,为什么呢?

Sandy 下午4:07

我晕,我觉的和电压容限有关系,但只是我猜的

win 下午4:08

@Sandy PCB设计 你说的memory down 是什么意思?科普一下

vivianwu 下午4:09

memory on board?

Sandy 下午4:09

是

Sandy 下午4:10

把颗粒直接做到板子上,而不是通过Solt接,Intel 这么叫

win 下午4:10

噢,我们直接在板上的也没有这几个电容

win 下午4:11

你这个图哪儿来的?去问设计人员

Sandy 下午4:11

大师 liyy 已经给了答案

win 下午4:12

不明白怎么跟随法?本来就是vdd分压来的,已经跟随vdd变化了

Sandy 下午4:12

求 liyy 不吝赐教

Sandy 下午4:12

应该是指电压波动的时候

黄跃辉 下午4:13

直流才是电阻分压,交流就不是了吧

Sandy 下午4:14

不是,应该是指VDD波动的时候,ref 跟随,微小的幅度

Sandy 下午4:14

我猜的

win 下午4:16

电阻分压,有纹波一样反应到下面的吧?你找个测一下就知道了

Sandy 下午4:17

我只是这样理解的

vivianwu 下午4:18

vivianwu 下午4:19

Understanding DDR3 VrefDQ and VrefCA signal waveform.pdf 三星

Sandy 下午4:19

@vivianwu0317 [强]

黄跃辉 下午4:20

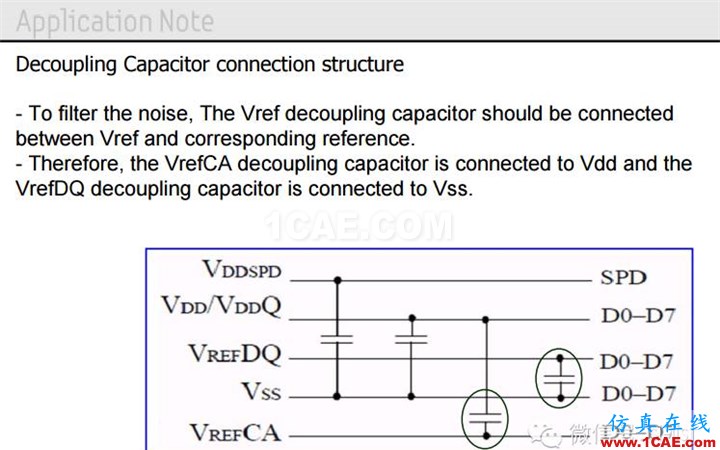

原来vrefca是以vddq做参考的

塞中 下午4:20

我的电源去耦电容优化optimizePI能仿真但没结果错在哪里?

win 下午4:21

去耦就对了,这个vrefca参考vdd是怎么来的

win 下午4:23

@黄跃辉 这句话怎么来的?芯片内部设计?二者参考不同?

塞中 下午4:23

电源平面对地的去耦

李yongyao 下午4:23

@Sandy PCB设计 vivian给出了很好的说明。vrefdq和gnd之间也有电容

Sandy 下午4:23

是 Vref DQ是接VSS的

Sandy 下午4:24

多谢vivian

黄跃辉 下午4:24

具体我也不太清楚,但是写的的确是在vref和相应的参考之间加滤波电容

vivianwu 下午4:25

應該感謝你 你不問 我也不知道 只知道 DDR3 有vreff_ca and vreff_dq 沒去想用途

黄跃辉 下午4:25

比如Vref DQ的参考室VSS

win 下午4:26

为什么vddca和地之间没有加电容

Sandy 下午4:27

@vivianwu0317 我原本以为 SCH错了呢,再对Jedec才发现的

win 下午4:28

这个是不是和芯片内部参考面怎么设计的有关

黄跃辉 下午4:28

我觉得是

黄跃辉 下午4:28

vddca可能是以vddq做参考的

win 下午4:29

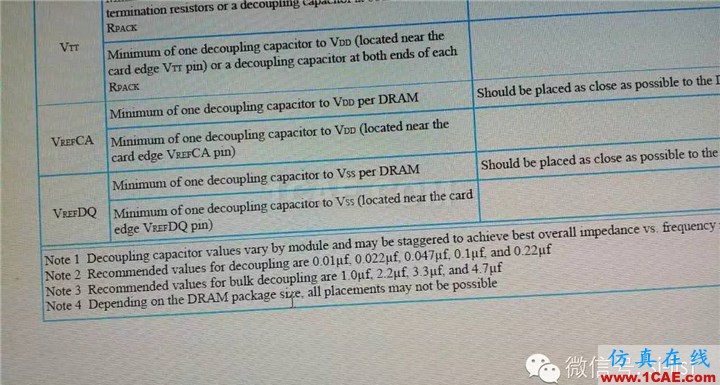

dimm卡也有这个要求的,我知道是去耦,不知道为什么

李yongyao 下午4:29

@win 你说的很对。不是所有的设计都需要这样

win 下午4:30

vivianwu 下午4:31

[强]

win 下午4:31

dimm卡也有这个要求,我感觉和芯片内部参考面分布来的

Sandy 下午4:33

是指颗粒内部设计?

Sandy 下午4:34

DDR 颗粒内部 ref 参考哪个平面,就和哪个平面退耦?

win 下午4:34

我感觉是

win 下午4:34

不知道有大牛懂吗

Sandy 下午4:35

让我想起部分设计 CA 是参考 VDD的,而DQ都是VSS

Sandy 下午4:36

@liyy 是指颗粒内部参考平面吗?

李yongyao 下午4:41

和ddr颗粒内部参考平面有关。但更主要的是因为cpu内部参考平面,ddr颗粒是跟随cpu走的

win 下午4:46

对,我觉得这个应该最初出自英特尔,

Colin 下午4:48

@liyy [强]大师分析的有道理

Sandy 下午4:50

@liyy 哦

Colin 下午4:52

如果芯片内部信号线参考电源 那PCB上最好也参考电源

Sandy 下午4:52

哦

李黎明 下午4:59

还有一个作用大家没谈到,电容跨接在两个电源平面上,可以为参考这个平面的信号线提供最短的回流路径,这些电容的摆放地点在layout时须注意!

Sandy 下午5:08

不是指电源平面,是指CA和DQ的参考电压

Sandy 下午5:08

ref_CA、ref_DQ

win 下午5:12

突然想到另一个问题,cpu那端也有vrefca和vrefdq吗?cpu那边应该不是分开的吧?

nevdie刘旭升 下午9:06

CA参考VDDQ是出于DIMM条考虑,CA信号处于DIMM条的中间,只有VDDQ pin提供参考。所以INTEL DIMM条的设计要求CA参考VDDQ,VDDQ与REFCA间的电容起跟随作用。DQ信号参考GND,VREFDQ与GND跨接电容就能起到跟随作用了。

win 下午9:15

@nevdie刘旭升 非dimm条的设计也要这样做的原因是什么

nevdie刘旭升 下午9:21

on board 我理解如果参考GND,加对GND的就可以了,但看过有设计是对GND和VDDQ都同时加电容的。

win 下午9:24

看样子又说不清了,别人memory on board也是这样设计,,,,大家说的都有点道理好像

邵鹏 下午10:05

关于DDR要求CAC参考VDD,DQ参考Gnd,是历史遗留问题。在最初设计DDR时(96年),芯片设计能力没有现在强,为了尽量减少芯片管脚,就强行规定CAC信号参考Vdd,这样有效地减少了Gnd管脚。随着技术发展,芯片封装尺寸越来越大,而且芯片内部电容也大量增加。实际上,现在对CAC信号要求参考Vdd已经没有实际意义,是Intel的设计习惯遗留。所以,现在的设计中参考什么都可以。

邵鹏 下午10:08

DDR4里面的VrefDQ和VrefCA又是另外一个问题,是因为CAC和DQ信号的驱动逻辑不一样。计划中等有时间我会写一个关于DDR的文章,把关于DDR设计中的一些疑问和一些误解全面解释一下。

乔健 上午11:50

大侠们,请教个问题

乔健 上午11:53

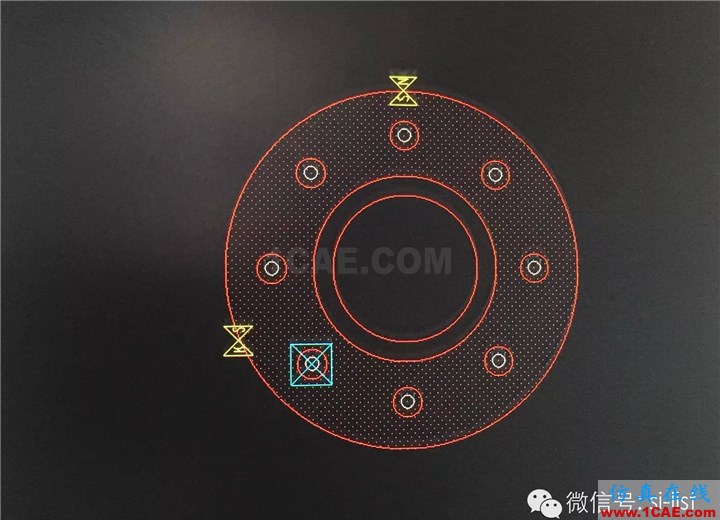

PCB上定位孔,直接接到板子上的地好?还是通过一个电容单点接地好呢?

胡 上午11:54

这是个经典问题,关注[呲牙]

荆棘鸟 上午11:55

见过直接的,也讲过串电容的

荆棘鸟 上午11:55

貌似后者好一些

李黎明 下午12:21

@乔健 这个问题不错?你自己有什么看法,还有你产品的使用环境,要过的标准是什么?

沈云峰 下午12:24

我遇到串电容辐射超标的

沈云峰 下午12:24

后来没办法,用电阻

乔健 下午12:55

我之前遇到一个项目,定位孔是悬着的.冬天,手一碰设备重启!静电问题

乔健 下午12:56

解决办法,地和定位空通过一个0.1电容连接

乔健 下午12:56

现在的设计定位孔全接地

乔健 下午12:57

静电都能过~

乔健 下午12:57

但不知道哪种方式更好~没找到评估的好办法

colordog 下午1:02

我的建议是直接连,但最关键的是保持一致

joy 下午1:04

@乔健 定位孔指的是固定螺钉的孔吗?

乔健 下午1:09

@joy 对

乔健 下午1:10

@joy 有研究过两种方式区别么?

joy 下午1:19

从我们的产品应用及EMC考虑,直接接地比较好

joy 下午1:19

但部分通讯的,规范交通类用的,是需要用电容隔离的

joy 下午1:20

轨道交通

梁骏 下午1:22

我有一个项目,机壳地与PCB地不串大电阻会干扰HDMI,引起电视机短时黑屏

joy 下午1:26

你HDMI的外壳是接机壳地还是PCB的GND,不同产品形态确实都有可能有独特的情况

李黎明 下午1:35

有个共性,产品上的地是要接在一起的!在这个前提条件下,抗静电,雷击,防止外部噪声入侵产品地平面,导致系统噪声过大,内部接地不好会导致产品emi辐射严重.

李黎明 下午1:39

有个极端例子,某通信户外产品,机箱上面只有一个螺丝孔(星月孔)这个好像被hw申请了专利,接在pcb的pgnd上,并且这颗螺丝的位置是在远离最容易尖端放点的位置.

李黎明 下午1:42

如果硬要串分立器件,个人不建议用电容

荆棘鸟 下午1:46

如何是好?

李黎明 下午1:48

个人见解,抛砖引玉……

李黎明 下午1:50

乔健 下午1:59

好滴~谢谢

乔健 下午3:14

@joy 轨道交通如果不加电容会发生什么问题?

joy 下午3:19

轨道交通,我们设备的外壳与列车外壳导通,在列车辫子通电时(具体术语忘记了),会有很大干扰通过地外壳,这种就有可能影响到设备内部数字电路。

Kate 下午3:34

@joy 信号地和外壳地直接分开呢?螺丝孔直接用npth这样。

乔健 下午4:18

相关标签搜索:DDR3 里 REF CA 和VDD之间接电容,有何作用?/PCB上定位孔,如何接地? HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析