走进台积电了解晶圆制造流程(视频分享)

2016-11-06 by:CAE仿真在线 来源:互联网

台积公司成立于1987年,是全球首创专业积体电路制造服务的公司。身为专业积体电路制造服务业的创始者与领导者,台积公司在提供先进的晶圆制程技术与最佳的制造效率上已建立声誉。自创立开始,台积公司即持续提供客户最先进的技术及台积公司 TSMC COMPATIBLE® 设计服务。

台积公司藉由与每个客户所建立的坚实的伙伴关系,稳定地创造了强而有力的成长。全球的IC供货商因信任台积公司独一无二的尖端制程技术、先锋设计服务、制造生产力与产品质量,将其产品交予台积公司生产。台积公司为约470个客户提供服务, 生产超过8,900种不同产品,被广泛地运用在计算机产品、通讯产品与消费类电子产品等多样应用领域。

2015年,台积公司所拥有及管理的产能超过900万片十二吋晶圆约当量。台积公司在台湾设有三座先进的十二吋超大型晶圆厂 (Fab 12, 14 & 15) 、四座八吋晶圆厂 (Fab 3, 5, 6 & 8) 和、一座六吋晶圆厂 (Fab 2),和两座后段封测厂 (advanced backend fab 1 and 2),并拥有二家海外子公司 WaferTech 美国子公司、TSMC中国有限公司及其它转投资公司之八吋晶圆厂产能支持。

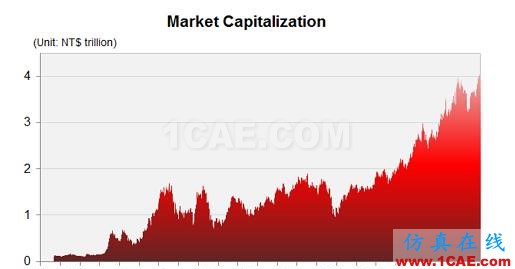

台积公司的全球总部位于台湾新竹科学园区,在北美、欧洲、日本、中国大陆、南韩、印度等地均设有子公司或办事处,提供全球客户实时的业务和技术服务;台积公司股票在台湾证券交易所上市,股票代码为2330,另有美国存托凭证在美国纽约证券交易所挂牌交易,股票代号为TSM。

1987年,张忠谋创立台积电,几乎没有人看好。但张忠谋发现的,是一个巨大的商机。在当时,全世界半导体企业都是一样的商业模式。Intel,三星等巨头自己设计芯片,在自有的晶圆厂生产,并且自己完成芯片测试与封装——全能而且无可匹敌。而张忠谋开创了晶圆代工(foundry)模式,“我的公司不生产自己的产品,只为半导体设计公司制造产品。”这在当时是一件不可想象的事情,因为那时还没有独立的半导体设计公司。

芯片生产工艺流程介绍

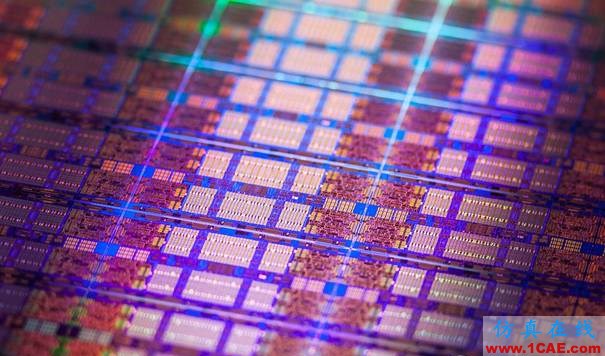

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1.晶圆处理工序

本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2.晶圆针测工序

经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3.构装工序

就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。其目的是用以保护晶粒避免受到机械刮伤或高温破坏。到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4.测试工序

芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。经测试后的芯片,依其电气特性划分为不同等级。而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。经一般测试合格的产品贴上规格、型号及出厂日期等标识的标签并加以包装后即可出厂。而未通过测试的芯片则视其达到的参数情况定作降级品或废品。

相关标签搜索:走进台积电了解晶圆制造流程(视频分享) HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析