使用Datasheet阻抗进行LDMOS匹配设计

2016-12-27 by:CAE仿真在线 来源:互联网

引言

本文档主要介绍了飞思卡尔在处理现今横向扩散金属氧化物半导体(LDMOS)器件所采用的阻抗数据表(Datasheet)的方法,其中LDMOS包括单端和推挽两种结构。此文的目的是阐明器件输入输出阻抗匹配网络数据表的使用。

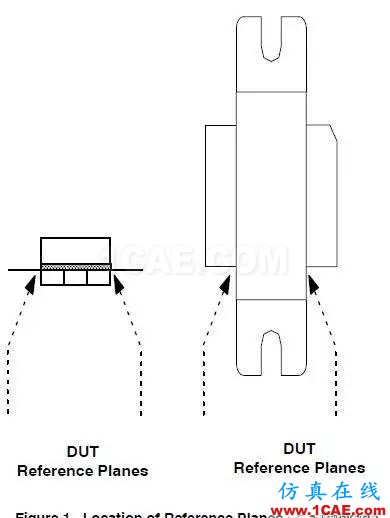

阻抗提取的方法有多种。本文档的范围不包括详细的提取方法;但介绍了一个可行的提取方法。无论使用哪种方法,主要关心的都是将去嵌入所提取的数据恢复到器件的参考平面的必要性,器件的参考平面如图1所示。

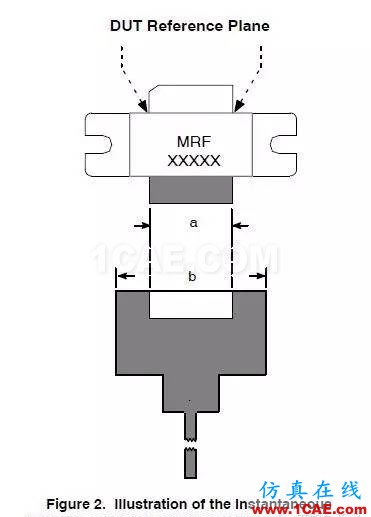

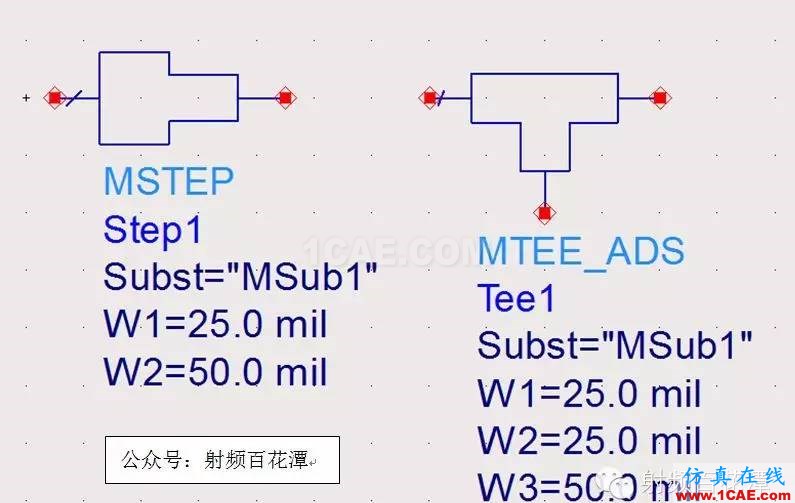

阻抗的提取需进一步求解MSTEP(Microstrip step in width)器件。是德科技ADS MSTEP仿真元件的用户展示出了基准平面宽度和铜线焊盘宽度之间的差异。例如图2就示出了铜引线焊盘宽度(“b”维度)比参考平面宽度(“a”维度)大。

有关此主题的更多信息,本文末尾的参考文献提供了一个严格且精确的阻抗测量方法。

单端器件

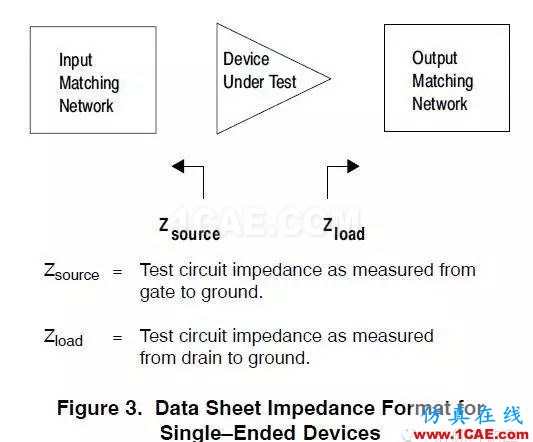

图3为单端器件的阻抗数据表形式。通过调谐夹具以得到器件的最佳性能,然后测得其在参考平面的阻抗,从而生成该器件的阻抗数据表。

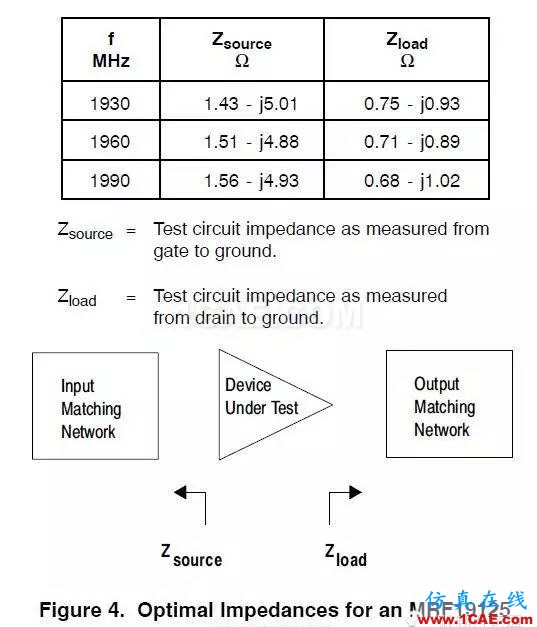

图4表明在使用频段内器件的阻抗随频段变化,数据表形式的阻抗特性可用于优化其性能。

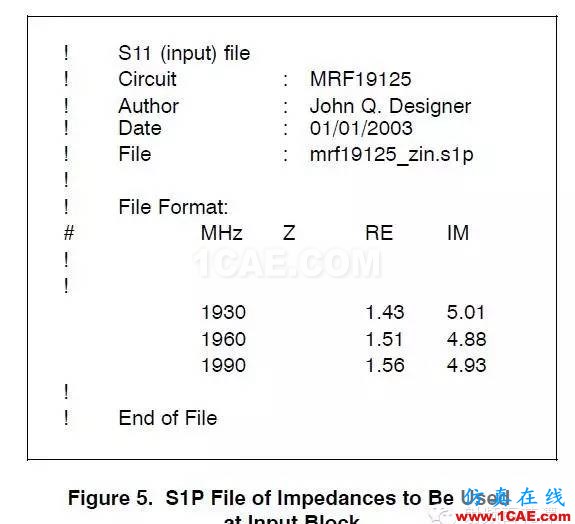

测得的数据可以转换成S1P文件,如图5所示。

注意:所测量的阻抗数据的虚部已被共轭化,如图4所示。

数据表中共轭化后的阻抗可用来计算阻抗的相对旋转偏移量。这表明,首次测得的阻抗是RF发射点处的视入值。然而,对于S11的优化则需要能够代表块的视入阻抗数据。这就是阻抗箭头重定向和共轭化阻抗数据的原因。

*对于所有主要参数,调谐后的最佳夹具将有总峰值性能;其中主要参数包括:输入回波损耗(IRL),效率,P1dB,线性,最大输出功率(Pout)和带宽。

注意:尽管一些史密斯圆图由于显示的原因而使用了不同的归一化阻抗值,但是在使用本工程公示中的阻抗数据时,设计师们应假定阻抗是基于50Ω系统。

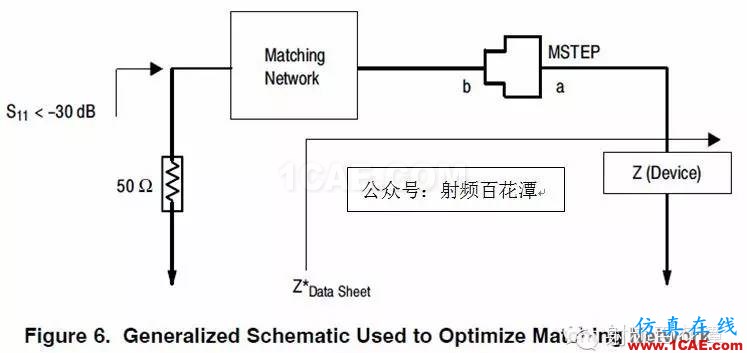

图6中的通用匹配电路将用于优化初步设计中的匹配网络。

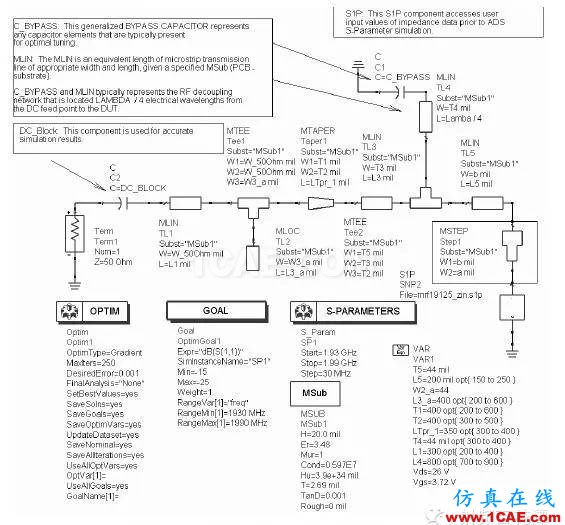

图5中的MRF19125阻抗数据是作为建立初步设计匹配网络的一个实际例子,匹配网络如图8所示。其中一些关键的细节如下:

•该S1P文件被用作一个双端口(基准为接地端口)器件并作为文件名的格式。

•该直流块和旁路电容只显示通用值。

•在理想情况下,从直流电源馈电到 DUT交界处的微带线应该有λ/ 4长。

•简化的C_BYPASS电容应尽可能的离微带线条近。

注:这里给出的是一个简单的匹配网络,它也可能被拓展成一个任何其他结构的拓扑电路。

前面已经讨论过的MSTEP必元件须放置在器件与第一匹配元件MLIN(放置位置的细节见图6,8,10和11)之间。MSTEP块极其重要,因为它被用于确定参考平面的宽度和铜引线焊盘宽度之间的差异。如果这些值不相同,阻抗将会不连续。MSTEP由其宽度值(“a”和“b”)确定。对于尺寸“a”的值,可以参照封装尺寸数据表。尺寸“b”是引脚将要焊接在PCB板上的铜焊盘长度。

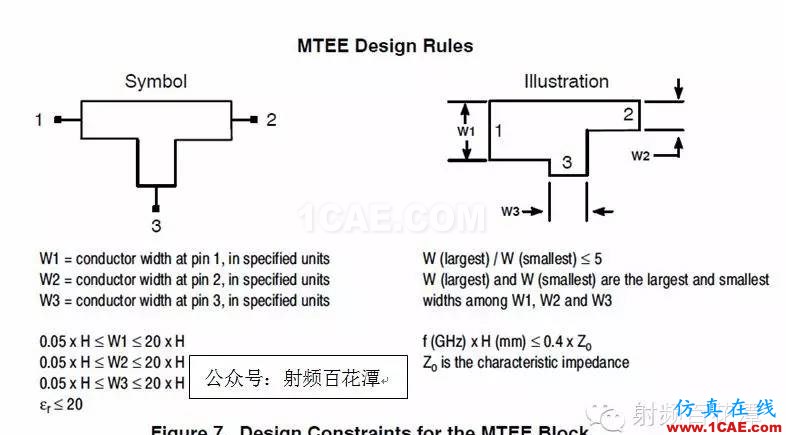

MTEE(Libra Microstrip T-Junction)是ADS的另一仿真元件,它用于连接的偏置馈给(参见图7)。该MTEE设计了违背典型的优化夹具布局的规则。一个简单的节点连接已足够准确地模拟阻抗。然而,如果可能的话,在它的使用限制范围内仍建议采用MTEE。

现在,阻抗数据已获得,共轭化后重新插入在了一个*.s1p文件里。下一步就是使用SP1块来优化仿真S参数,如图8所示。匹配网络S11应调谐到至少-30 dB(或尽可能低),则第一个输入匹配电路就完成了。重复这一过程,利用输出阻抗来完成输出匹配,。最后,该匹配网络将在印制电路板PCB上实现。

推挽式器件

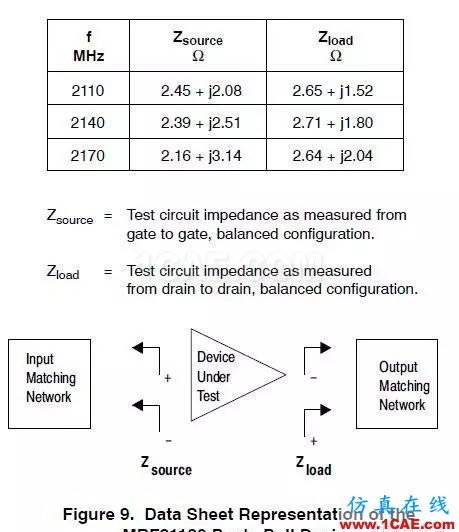

推挽式器件获取阻抗的方法与单端器件从固定夹具上获取阻抗的方法类似.其具有代表性的阻抗值如图9所示.

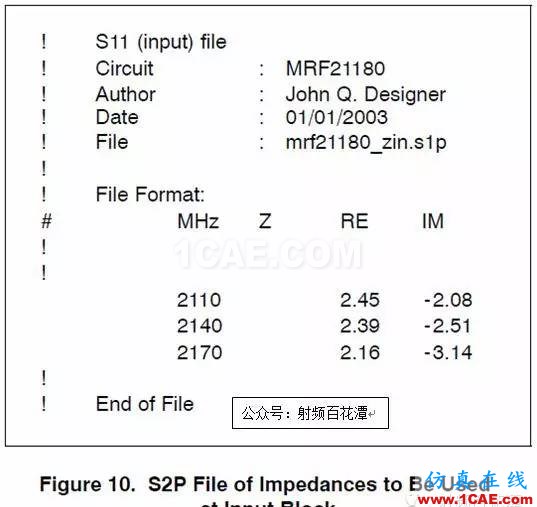

推挽式器件阻抗数据应在数据存储装置中显示出来,图10展示了一个范例。

注意:图9中的测量阻抗数据的虚部已被共轭化,这与单端器件的处理方法相同。

用于初步设计优化推挽式器件输入和输出端匹配网络的方法和单端器件的相同。

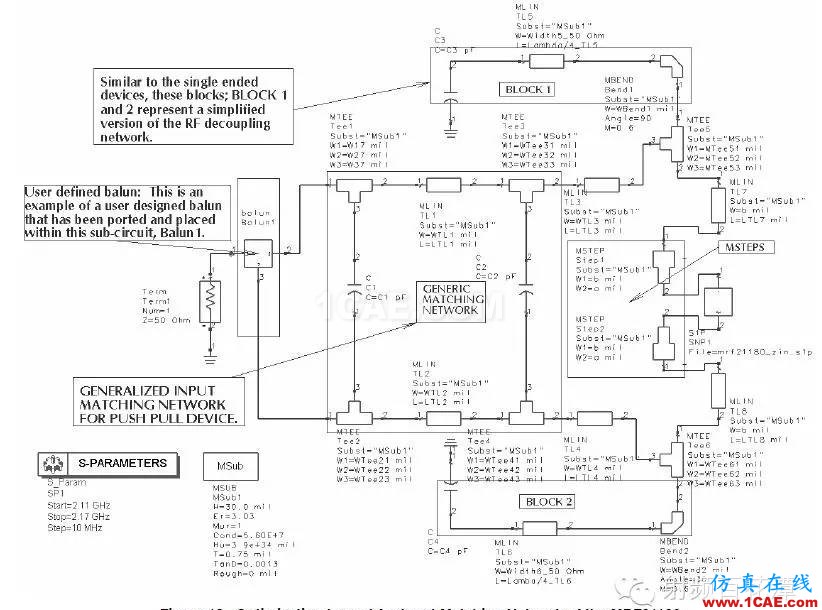

图11示出了用于初步设计优化输入匹配网络的电路。图11所示的平衡-不平衡巴伦是一种理想化的三端口器件,通常其输入/输出的阻抗比为n:1。

图12展示了主要模块:

•通用匹配网络

•直流电源馈电块1和2

•MSTEP块

•用户定义的三端口子电路(巴伦)

•两端口*.s1p

在一个好的初步设计中,图12所示的通用匹配网络代表了典型可实现的电路元器件组。网络的拓扑结构不限于图12所示的这一种。这个拓扑结构只是一个典型的设计。

这两个直流馈电块和MSTEP块与图7 单端器件的类似,它们有着相同的功能。

图12中的这个三端口子电路可以是ADS里(用户可以设计)的巴伦,或者是由Sonnet 或一款类似电磁仿真仿真软件生成的*.s3p文件。

两端口的S1P数据块文件代表了MRF21180共轭化后的阻抗数据。这个块有两个端口代表了共轭化后的阻抗,另外第三个端口是参考地。

结论

这个工程公示文档给出了一个关于怎样基于实测阻抗数据完成匹配结构的简明方法。尽管还有其他的解决办法,但使用这个方法可以为设计师的最终设计提供一个好的近似值。

引用文献

J.J.Bouny, “Impedance Measurements for High Power RF Transistors Using the TRLMethod,” MicrowaveJournal, October 1999。

原文作者:Darin Wagner ,Freescale

相关标签搜索:使用Datasheet阻抗进行LDMOS匹配设计 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析