高速电路上过孔的优化(高速电路设计工程师不容错过的基础知识)

2017-01-19 by:CAE仿真在线 来源:互联网

在边沿速率是ps级的高速串行链路中,通道任何的阻抗不连续都会影响到信号完整性。通道不连续的原因很多,其中最常见的一个就是信号过孔。过孔会带来抖动,使眼图变小,最终导致接收端误码。

本文讨论了传输线上过孔的不连续性和怎么去减小过孔的影响。我们经常用TDR和全波3D电磁场仿真软件去评估过孔阻抗、插入损耗Insertion Loss和回波损耗Return Loss以及对信号带来的影响。

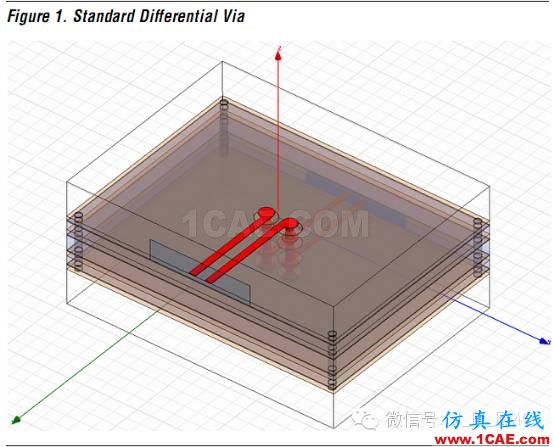

Figure1是高速链路上典型的差分过孔。过孔包括pads,drill,unused pads和anti-pad.下图中,100ohm的差分线从top层换到layer6,layer6到layer8就留下一个过孔残桩(stub),layer3和layer8还有两个NFPs(non-functionalpads).

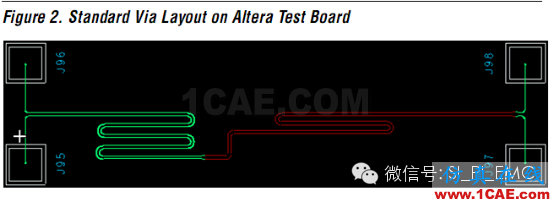

Figure2是一个测试板,我们会用这个测试板去做HFSS建模和测试的对比。在top层走了5inch的蛇形线(green),然后换到layer6继续走了5inch走线(red). J95~J98是SMA连接器。

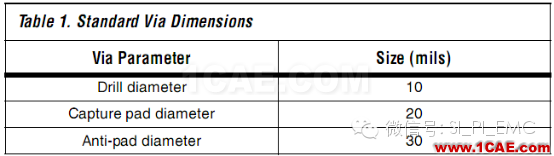

Table1列举了过孔的尺寸,是一个常见的标准过孔。后续的仿真会在这个标准尺寸上做优化。

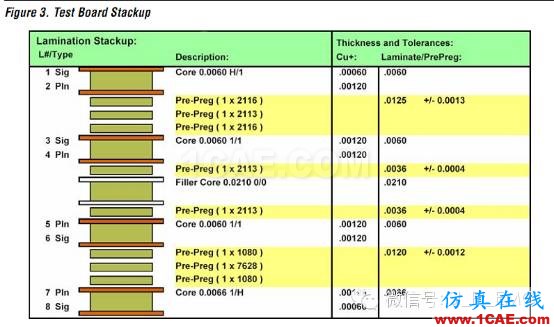

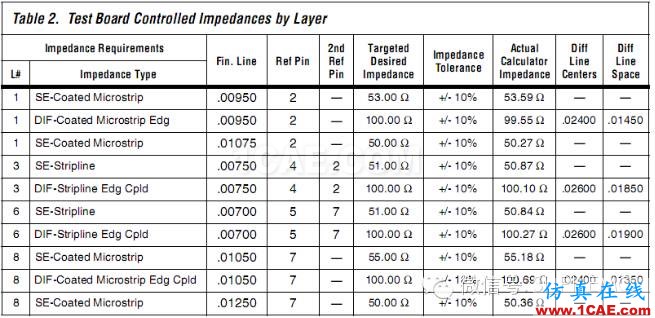

Figure3是测试板的叠层。Table2是目标阻抗是100ohm +/-10%的走线尺寸。在用仿真去优化这个过孔之前,我们先要去做HFSS过孔仿真和测试的校准。

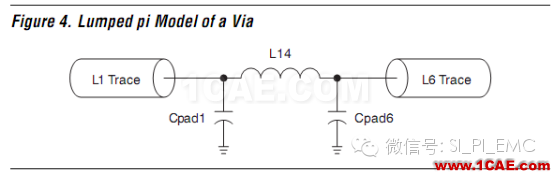

过孔有容性和感性效应。这些容性感性寄生参数会导致通过过孔的信号衰减退化。Figure4是一个简单的L,C集总模型,尽管这个模型只适用于过孔时延小于1/10信号上升时间的情况,但它对于去理解过孔的感性容性效应仍然是有用的。

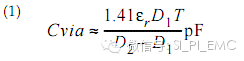

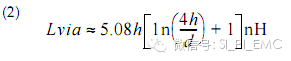

如果把过孔看作LC集总模型,它的容值和感值可以通过以下公式来计算:

其中,ε代表介电常数,D1是过孔pad的尺寸,D2是anti-pad的尺寸,T是PCB的厚度,h是过孔长度,d是过孔孔径大小。

从式1可以看出来,要想减小过孔的容性效应,就要减小过孔pad,加大anti-pad,类似的,减小过孔长度可以减小其感性效应。

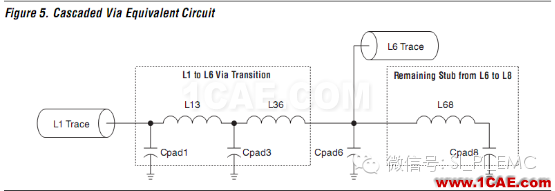

Figure1的等效模型可以用Figure5的级联模型来表示。信号从top层换到layer6,遇到每一个pad都会有电容效应,每一段长度都会贡献电感。在这个例子中,Cpad1,Cpad3,Cpad6和Cpad8代表了layer1,3,6,8 pad的电容;类似的,L13,L36和L68代表了从layer1到layer3,layer3~layer6,layer6~layer8的过孔电感。L68和Cpad8表示layer6以下的stub.这些电容、电感和stub的寄生参数都会造成信号的退化。

尽管式1和式2不能直接用在这个等效模型上,但是减小过孔电容和电感的方法还是一样。我们用HFSS作了一些优化去评估过孔的阻抗和S参数,包括:

减小Cvia:减小pad大小;去掉NFP;加大anti-pad

减小Lvia:去掉stubs;尽量表面布线以减小过孔长度或用背钻。

我们做了以下case的TDR和S参数的对比:

1, Layer1 to layer3(long stub)

2, Layer1 to layer6(short stub)

3, Layer1 to layer8(no stub)

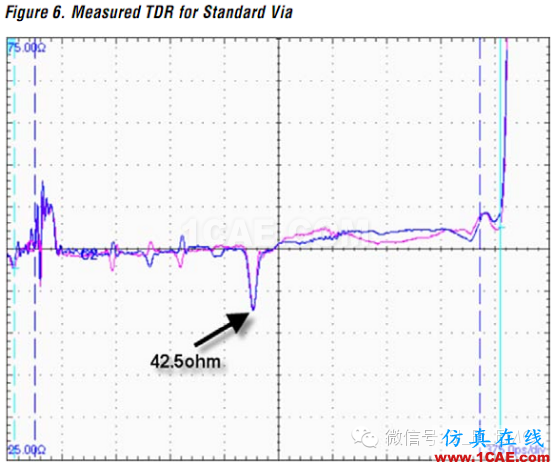

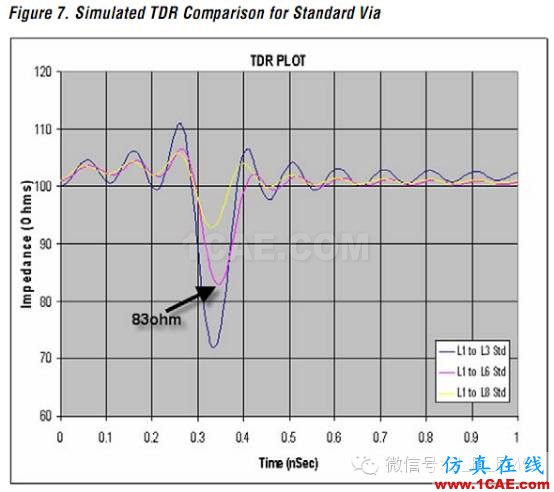

Figure6是用TDR测出的layer1到layer6过孔的阻抗,我们用这个过孔来做测试和仿真的校准。测试显示测试板上的过孔的奇模阻抗是42.5ohm,如果是对称的差分线,其差分阻抗是奇模阻抗的两倍,也就是85ohm. 这个过孔差分阻抗我们仿真出来的结果是83ohm(如Figure7)。测试和仿真结果一致后,我们就可以放心地用HFSS去做过孔优化了。

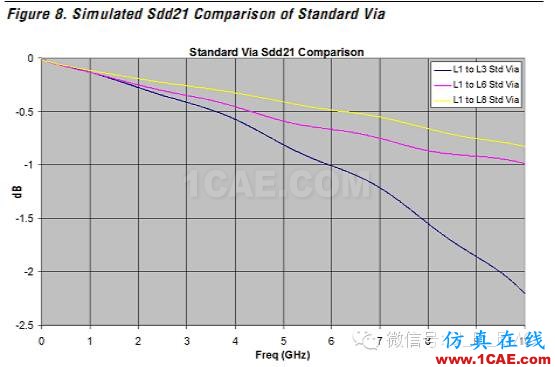

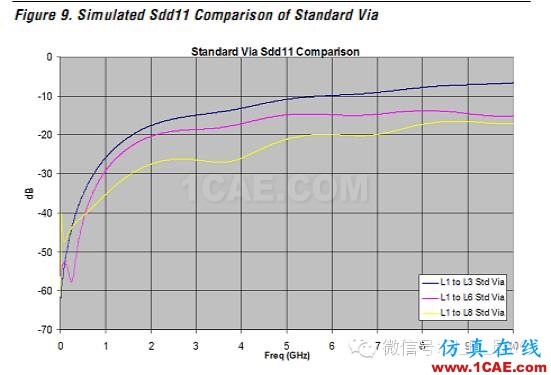

Figure 8和9对比了用HFSS仿真出来的这三种情况的插损和回损(Sdd21和Sdd11)

从Figure 7到10可以看出,更长的过孔stub会带来更大的阻抗不连续,损耗更大。你可以只在top或bottom布线去避免过孔stub. 然而由于布线空间制约,EMI的一些考虑等,还是要将走线布在内层,这时时候就必须去考虑过孔的优化。

如式1和式2,要减小过孔影响,必须减小Cvia和Lvia。正常来说,由于布线空间限制,过孔pad已经做到最小,所以用以下优化策略:

1,去除NFP;

2,加大anti-pad尺寸;

3,去掉/减小过孔残桩;

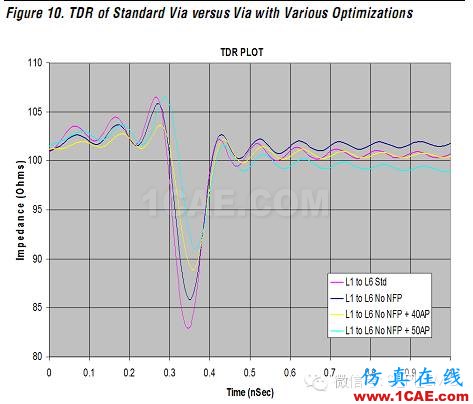

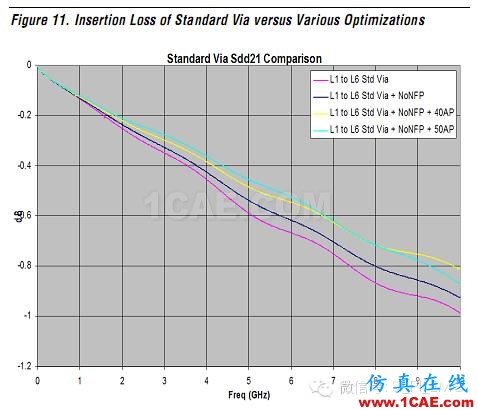

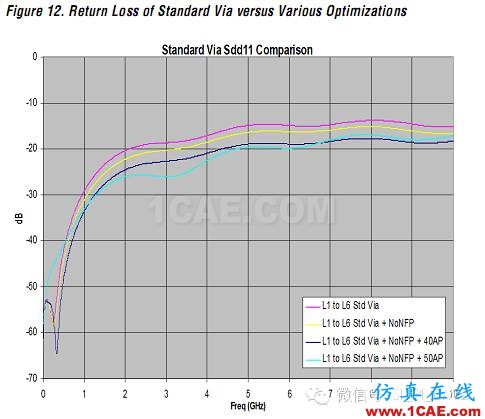

Figure10~12对比了TDR,插损和回损的仿真结果,在图中:

1,“L1 to L6”代表信号从layer1变换到layer6;

2,“No NFP”代表去除所有的no-functionalpads;

3,“40AP”和“50AP”代表过孔的anti-pad从标准的30mil加大到40/50mil

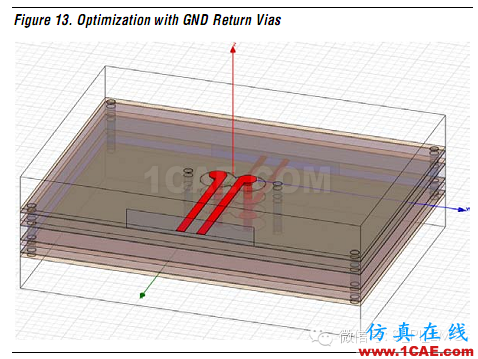

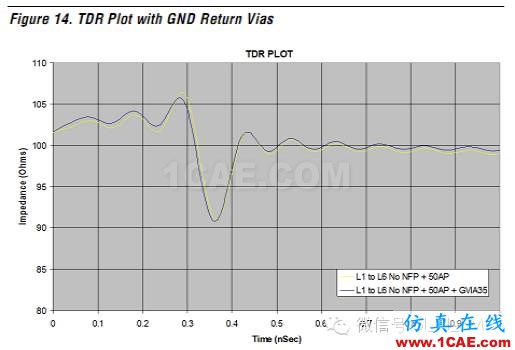

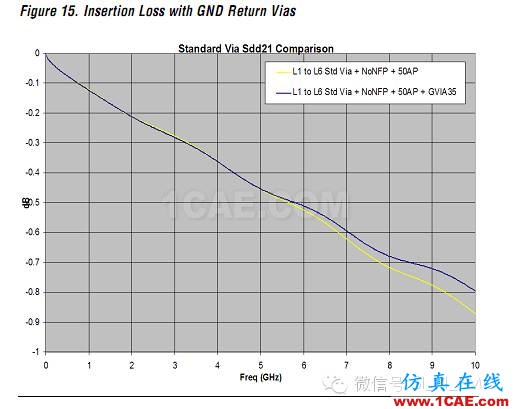

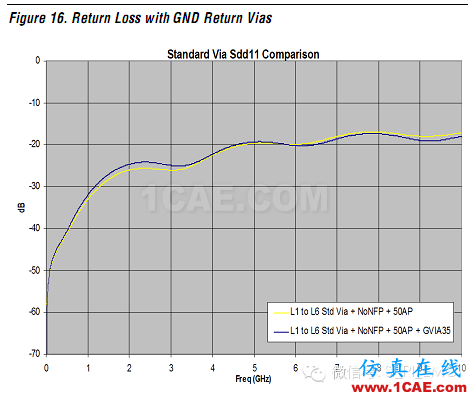

另外一个方法就是在信号过孔邻近加地孔,给过孔提供一个好的回流路径,如Figure13~16所示。加地孔对阻抗,插损和回损都有改善:

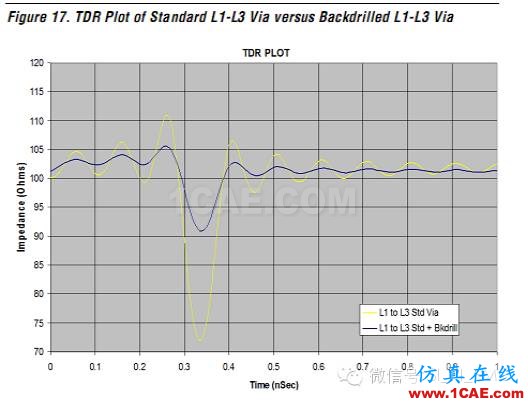

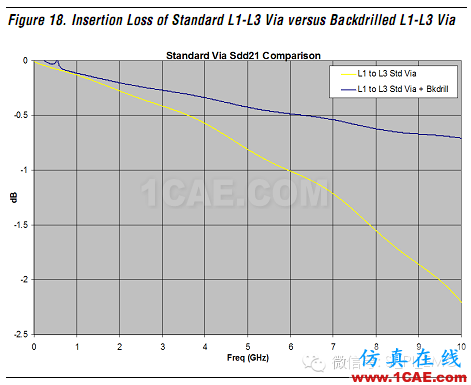

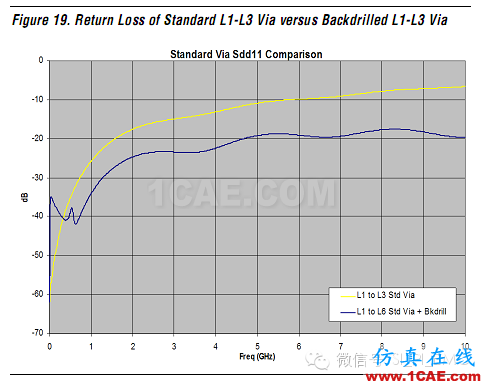

另外一个优化过孔的方法就是用背钻或PCB背面埋孔方式去去除过孔的残桩,这种方法的成本比较高。仿真的TDR,IL和RL波形如Figure17~19所示,如果过孔的stub很长,用背钻会有明显的改善。

过孔的设计一直都是高速设计的一个坎,特别是当信号超过5GHz的频率之后,已经变得非常难以控制。所以大家在产品正式设计时,尽量做好仿真和测试研究,以便在项目中尽量减少问题。

相关标签搜索:高速电路上过孔的优化(高速电路设计工程师不容错过的基础知识) HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析