差分信号剖析与探讨

2017-03-24 by:CAE仿真在线 来源:互联网

Introduction

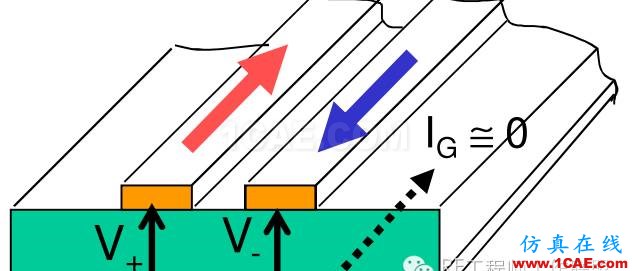

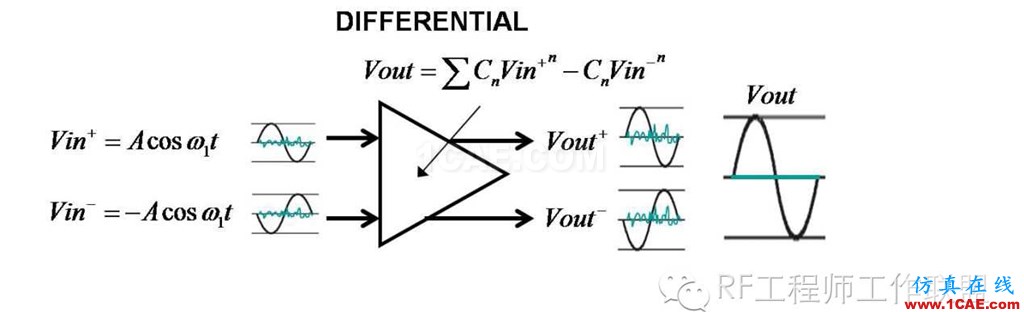

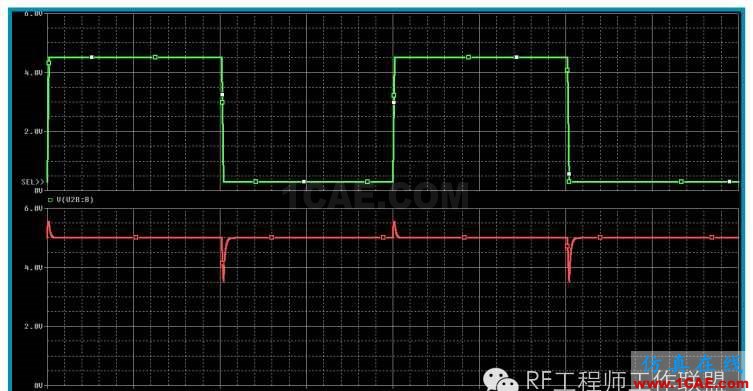

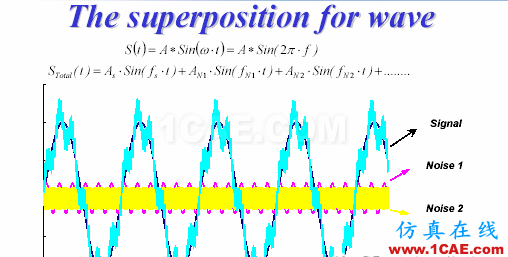

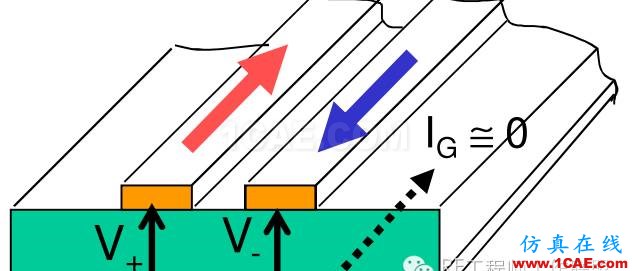

驱动端发送两个大小相等,方向相反的信号,接收端会有一个相减器,比较

这两信号的差值,来判断逻辑位是0 或是1,此即所谓的差分讯号[1]。

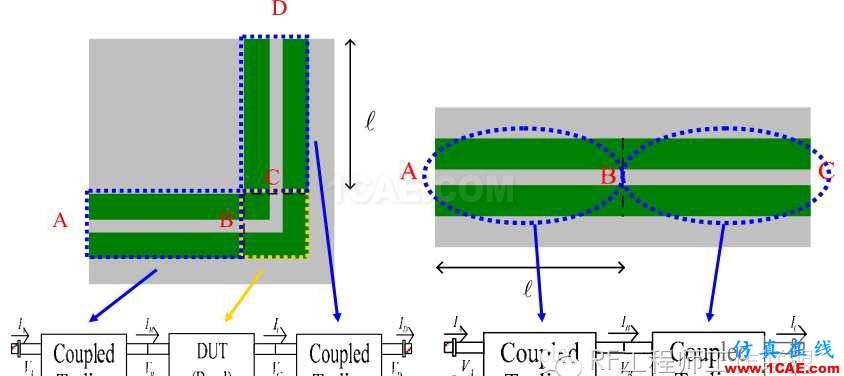

而下图是实际PCB 的差分走线[1]。

1

Advantage

使用差分讯号的第一个好处,就是具错误更正效果[2]。

2

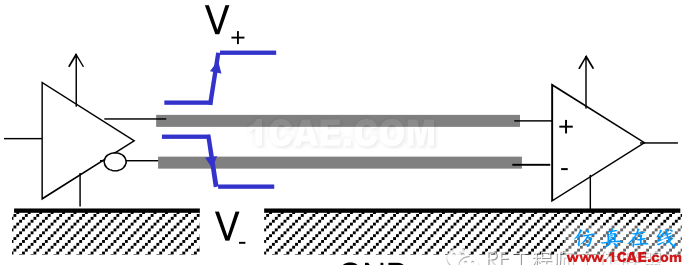

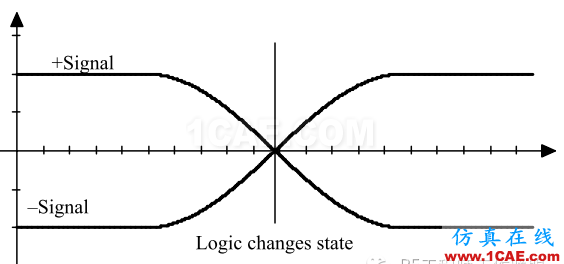

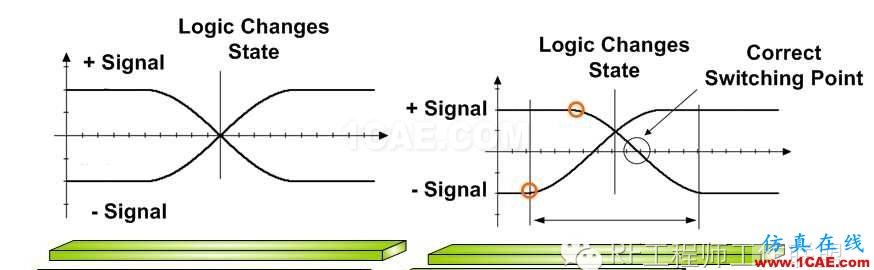

由于差分信号的逻辑判断,是仰赖两个信号的交点,如下图[4] :

图片[7] :

3

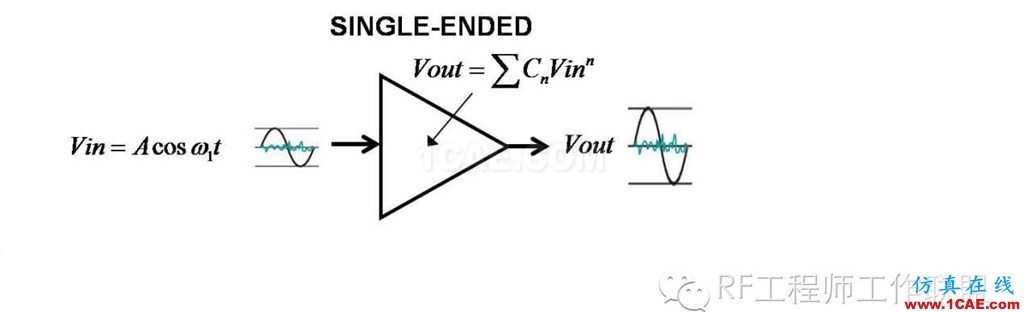

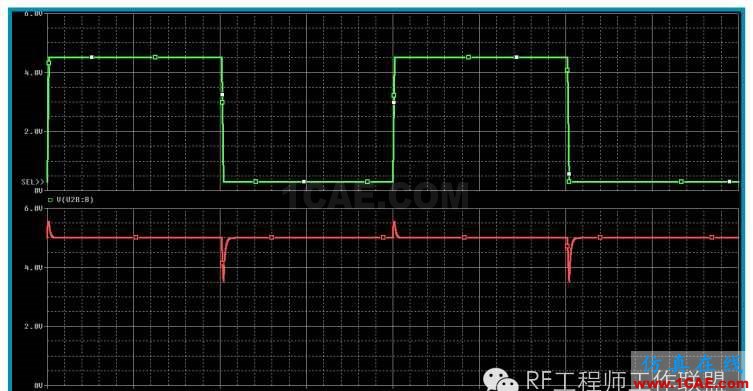

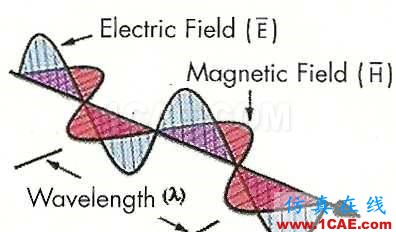

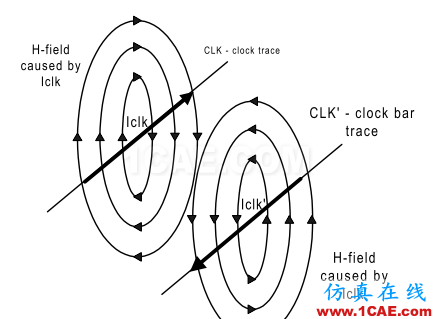

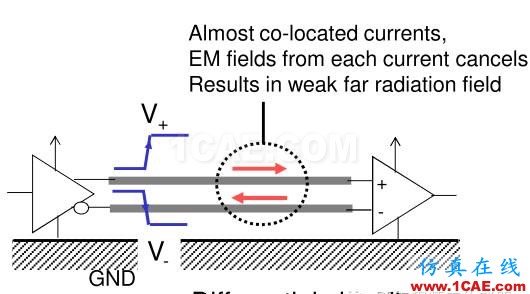

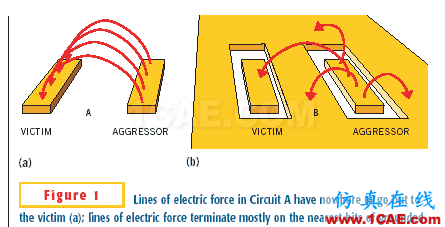

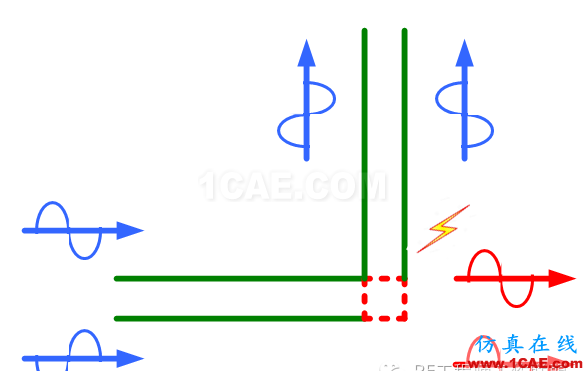

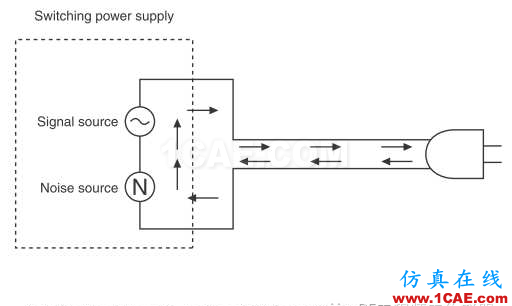

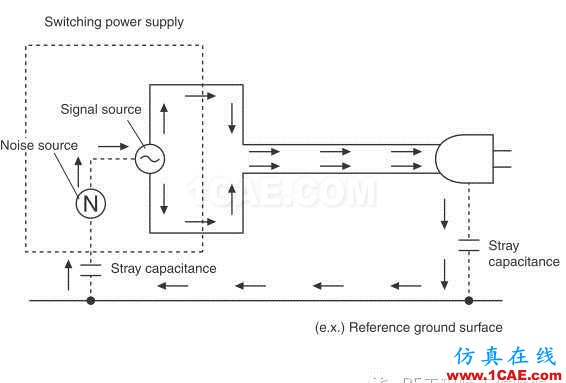

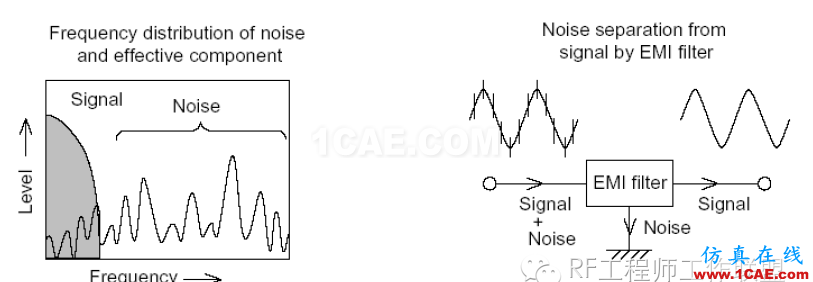

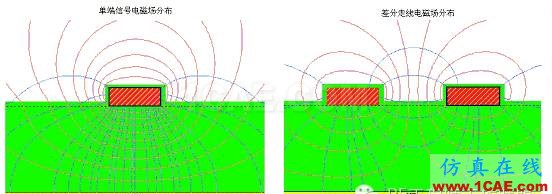

第二个好处,可以有较小的EMI 辐射干扰,由于数字信号在逻辑切换时,会

因电压变换产生电场,进而产生EMI 辐射,对邻近走线造成干扰[9,15],如下图

[12] :

4

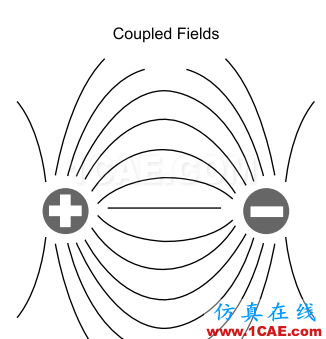

而差分讯号所产生的磁场,会彼此相消,所产生的电场,会因彼此紧密地耦合在一起,进而减少发散向外的机会[8-10]。

由于差分讯号可以减少磁场份量,以及减少发散向外的电场,进而降低EMI 辐

射干扰,这也是为什么高速数字讯号一般都用差分讯号[1]。

5

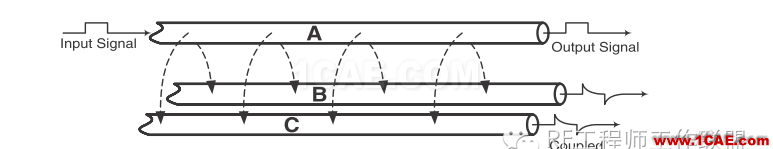

而差分讯号除了可以产生较小的EMI 辐射干扰,同时也具备了较佳的抗干扰能

力[16-17],我们以下图说明 :

量耦合到B 跟C,以S 参数表示,A 耦合到B 为SBA,A 耦合到C 为SCA。当B

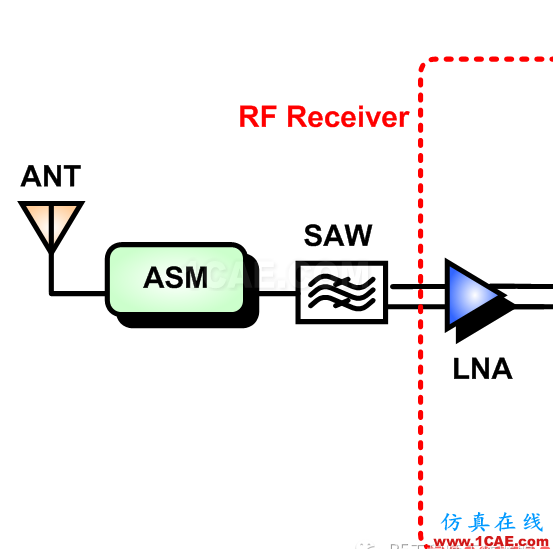

跟C 很靠近时,则SBA = SCA,而又因为B 跟C 的讯号方向相反,所以SBA 跟SCA是等量又反向,亦即彼此相消,这就是为何差分讯号拥有较佳的抗干扰能力。而在射频电路中,相较于发射讯号,接收讯号多半很微弱,因此其接收路径多半采差分型式,以便获得较佳的抗干扰能力,避免灵敏度下降。

6

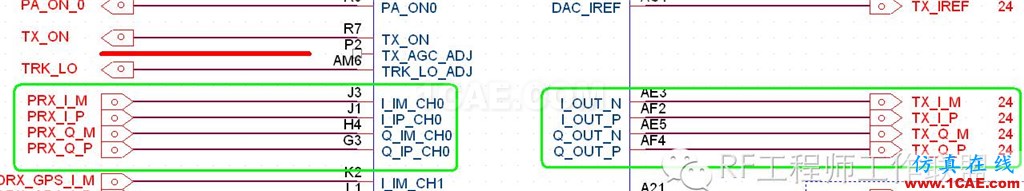

而为了得到良好的频谱利用率,到了数字通讯时代,多半会利用IQ 讯号,来达

到SSB (Single-Sideband) 的调变方式[16],而因为IQ 讯号会影响到调变与解调

的精确度,因此不管是发射还接收电路,其IQ 讯号都会走差分形式,避免调变

与解调精确度,因噪声干扰而下降[16]。

7

Length

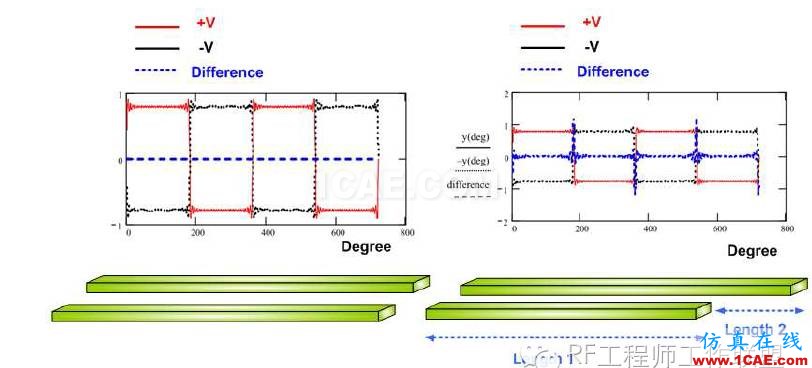

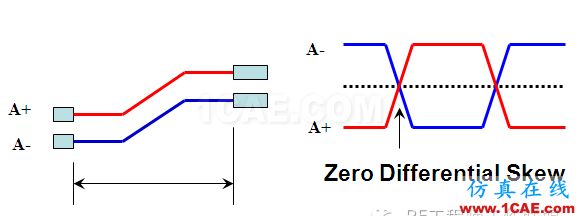

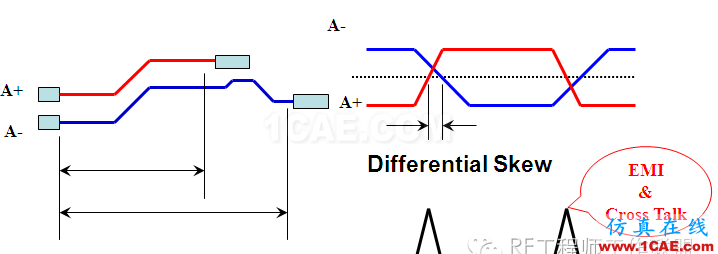

由前述已知,差分信号的逻辑判断,是仰赖两个信号的交点,因而受工艺,温度的影响小,能降低时序上的误差,如下图左。然而倘若该差分信号长度不相等,则会因相位差之故,导致切换电压的时间点不同,如下图右的黄圈处,进而使得逻辑判断错误[4]。

8

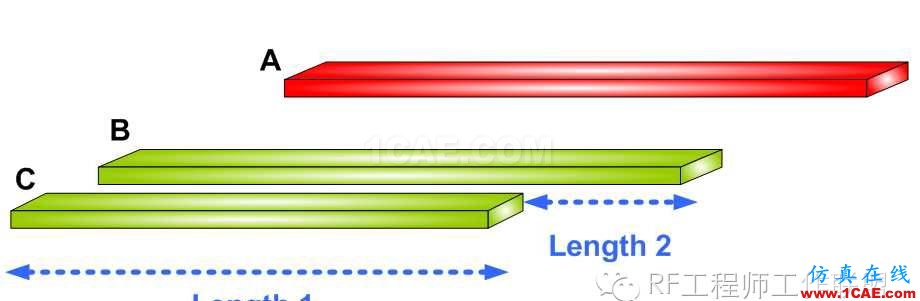

但差分讯号所产生的电场,会因彼此紧密地耦合在一起,进而减少发散向外的机会,进而减少EMI 幅射干扰,如下图左。然而倘若该差分信号长度不相等,如下图右,此时Length 2 为一单端讯号,亦即逻辑切换瞬间所产生的电场,会发散向外,产生EMI 辐射干扰。若Length 2 越长,表示该差分讯号的相位差越大,其切换噪声的脉冲宽度就越宽,维持时间就越长[4]。

同时也由前述已知,邻近噪声对差分讯号的耦合量,会彼此相消,因而提高抗干扰能力,然而倘若该差分信号长度不相等,如下图,则此时Length 2 为一单端信号,A 耦合到Length 2 的能量无法消除,亦即B 会很容易被A 干扰。

9

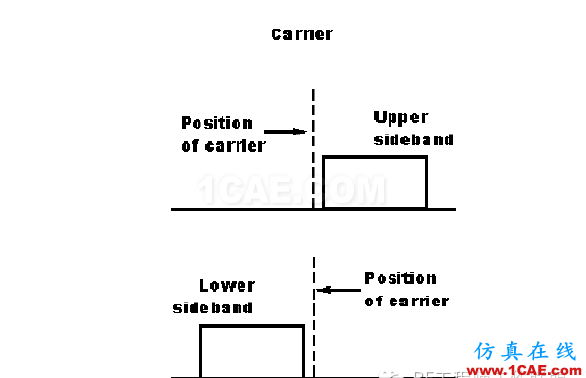

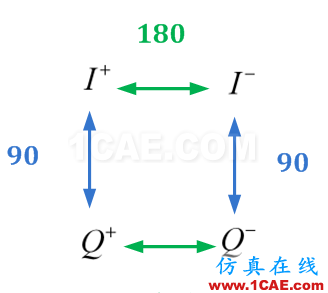

而前述已知,为了得到良好的频谱利用率,到了数字通讯时代,多半会利用IQ

讯号,来达到SSB (Single-Sideband) 的调变方式,亦即频谱上只能有一个

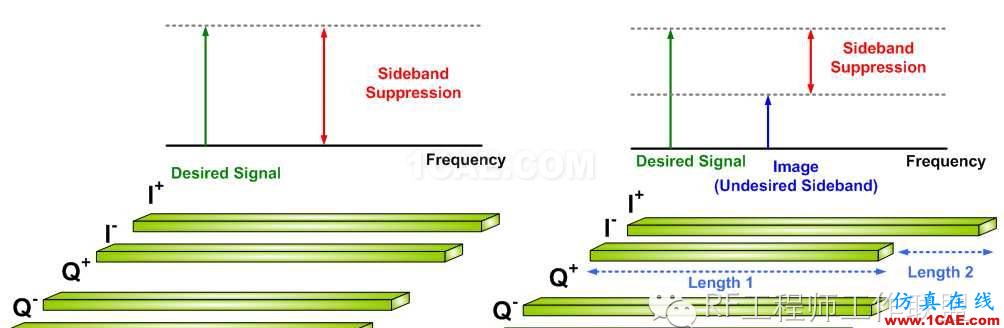

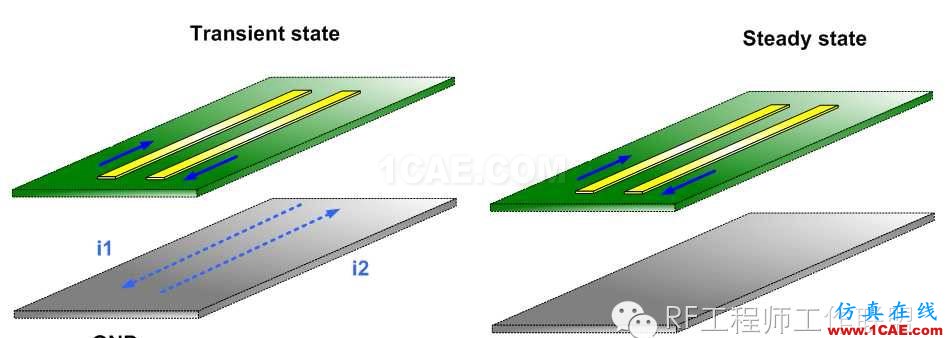

Sideband,如下图[16] :

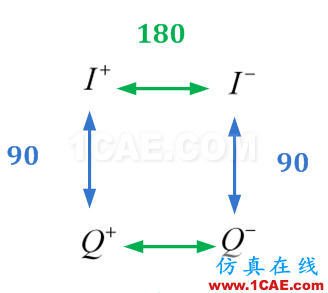

会有I+、I-、Q+、Q- 四条讯号,如下图 :

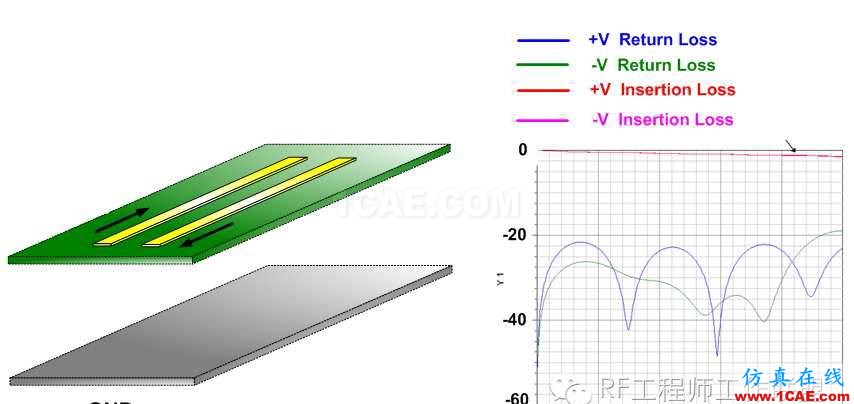

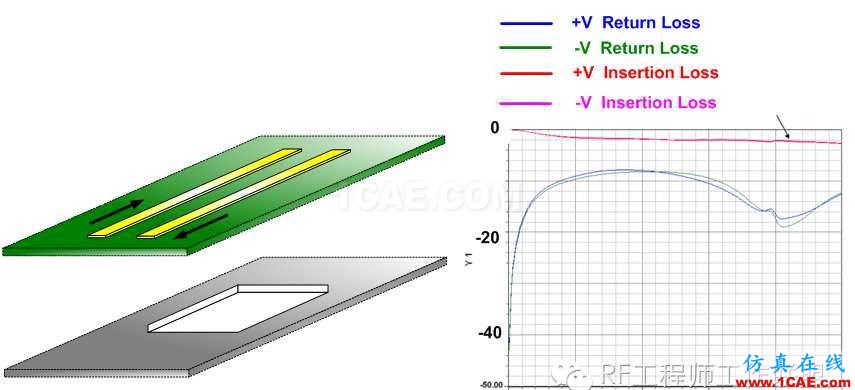

10

由[16]可知,I+、I-、Q+、Q- 四条讯号线都必须等长,才能确保IQ 讯号相位差

为90 度,此时便如前述,频谱上只出现了一个Sideband,如下图左。而只要有

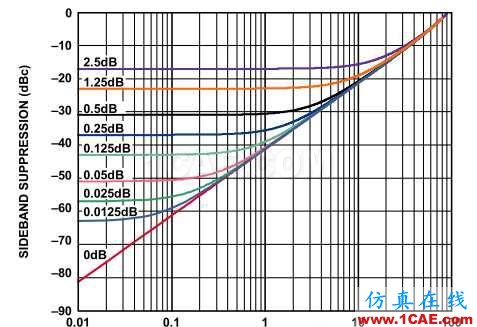

任一讯号线不等长,那么IQ讯号相位差就不为90度,则称为IQ phase Imbalance,在频域上,会出现另一个我们不要的Sideband,称之为Image,如下图右[20]:

而Image 与主频讯号的振幅差,称之为Sideband Suppression,若上图右的Length2 越长,则IQ phase Imbalance 就越大,亦即Sideband Suppression 就越小。反之,若四条讯号线都等长,亦即完全没有IQ phase Imbalance,那么理论上会完全无Image,如上图左。

11

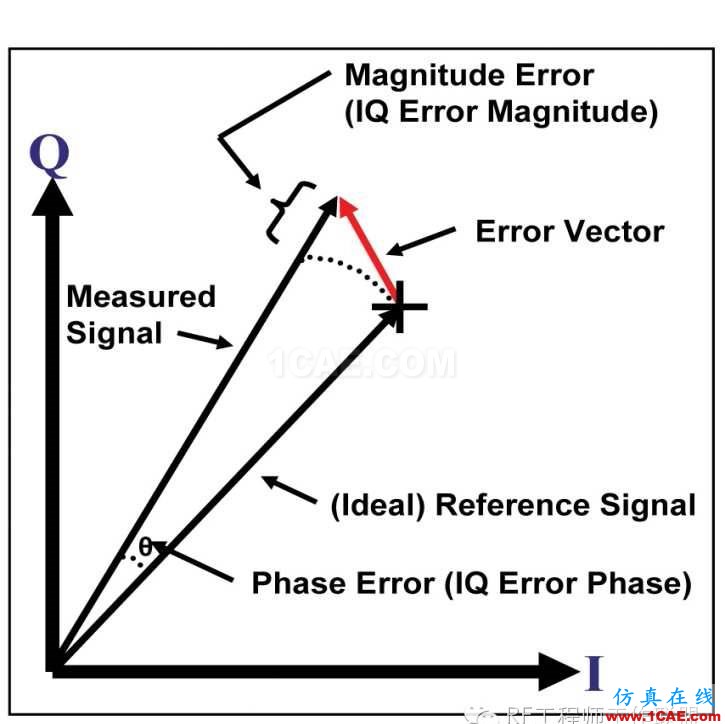

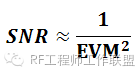

而由[16]可知,解调时,会以所谓的EVM(Error Vector Magnitude),来衡量IQ

phase Imbalance 的程度,如下图 :

亦即若前述的Length 2 越长,那么IQ phase Imbalance 越大,则EVM 越大,SNR越小,灵敏度就越差。

12

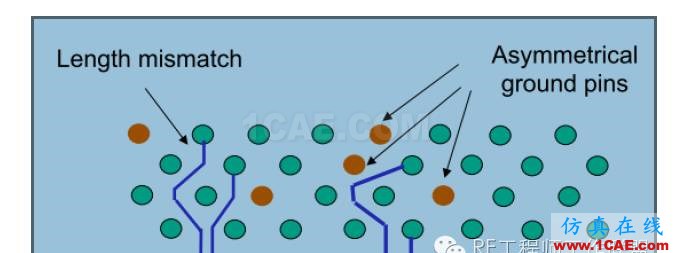

以上皆为差分讯号若不等长的影响,因此,在设计差分讯号时,最重要的就是要等长,越是高速讯号,越要注意等长[5-6]。然而实际上,有可能因为IC 的Pin

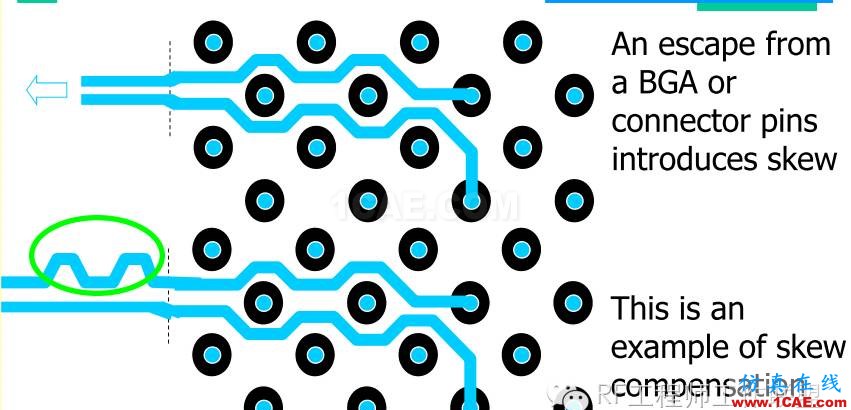

位置关系,使得差分讯号会不等长[26]。

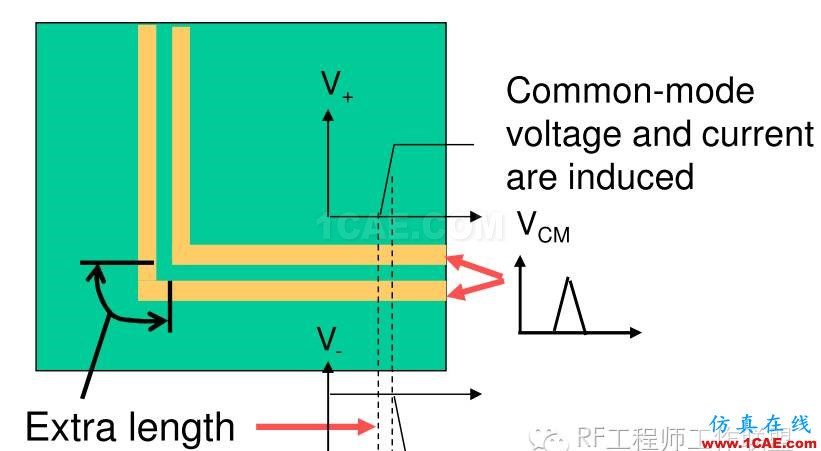

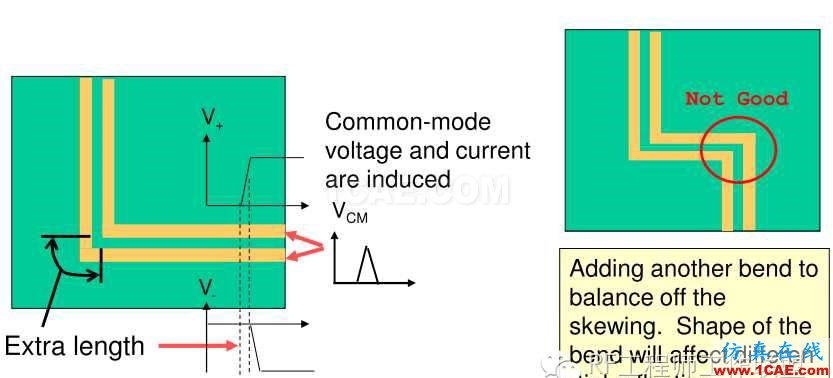

或是会因为转弯缘故,使得外侧走线会多出额外的长度,导致相位差,因而产生额外的共模噪声[26]。

13

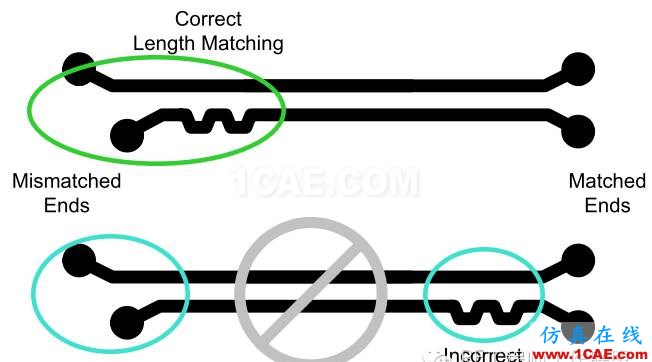

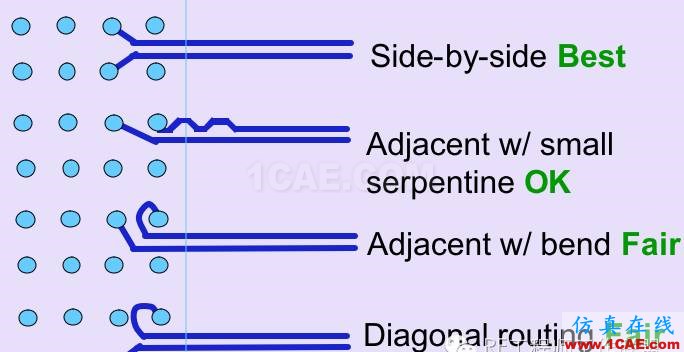

因此通常会针对长度较短的走线,用所谓的蛇状线,额外再增加长度,使其差分讯号达到等长的目的,如下图[2] :

14

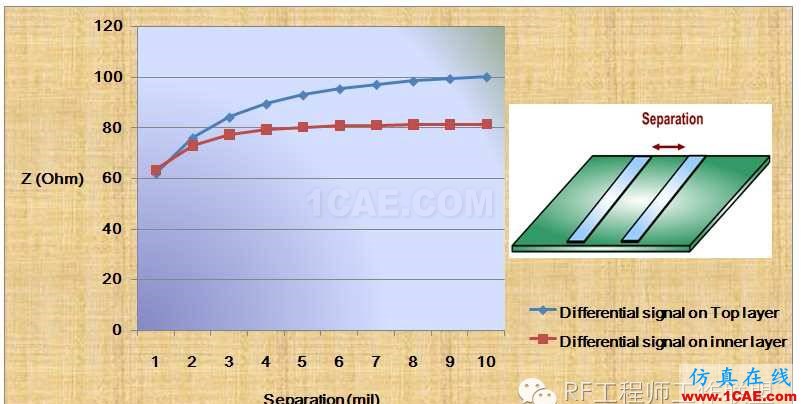

Separation

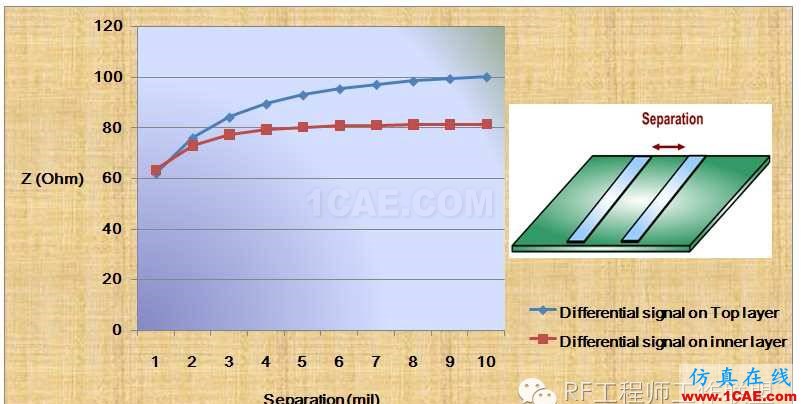

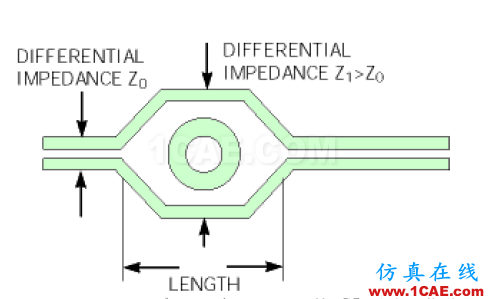

由[23]可知,差分讯号的阻抗,与间距会有关系,如下图[27] :

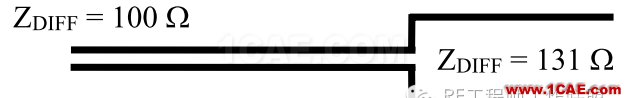

因此差分讯号的间距要维持固定,否则会因阻抗不连续而产生反射,进而导致

EMI 幅射干扰加大[12]。

15

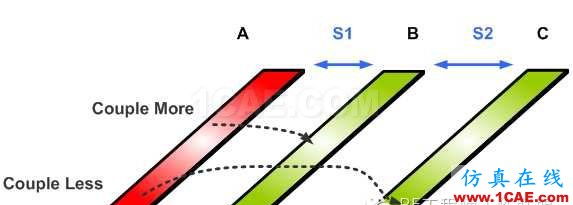

另外,差分讯号的间距,不只与阻抗有关,也牵扯到抗干扰能力,我们以下图作说明。

B 跟C 为差分讯号,而A 为邻近的讯号,当A 跟B、C 靠得很近时,亦即S1 很

小时,A 会把能量耦合到B 跟C,以S 参数表示,A 耦合到B 为SBA,A 耦合到

C 为SCA。如果B 与C 靠得很近,亦即S2 很小,则SBA = SCA,而又因为B 跟C的讯号方向相反,所以SBA 跟SCA 是等量又反向,会彼此完全相消,因而将A 对于B、C 的干扰降到最低。然而,若B 与C 离得很远,亦即S2 很大,则SBA > SCA,那么SBA 跟SCA 便无法完全相消,此时B 会受A 的干扰。由此可知,若差分讯号要具有最佳的抗干扰能力,则间距必须越小越好。当然,由前述可知,间距越小,其阻抗就越小,这会使阻抗无法控制得宜,因此,更精确一点讲,在符合阻抗控制的前提下,其间距必须越小越好,这样才可有较佳的抗干扰能力。

另外由前述可知,差分讯号可以减少磁场份量,以及减少发散向外的电场,进而降低EMI 辐射干扰。然而,倘若S2 过大,则磁场无法完全相消,且彼此间所产生的电场,也会因耦合量降低,进而增加发散向外的电场,导致EMI 辐射干扰加大,因此,在符合阻抗控制的前提下,其间距必须越小越好,这样才可有较小的EMI 辐射干扰。

16

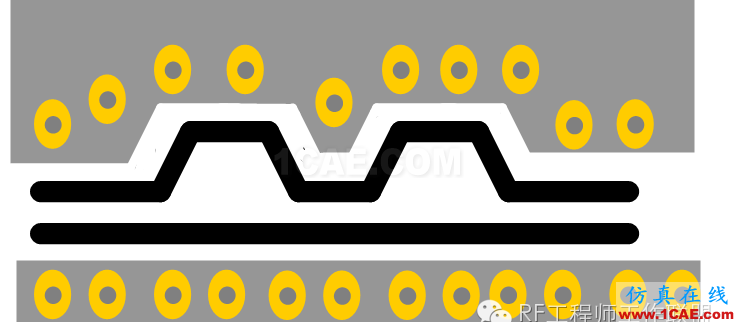

而前述提到,因此通常会针对长度较短的走线,额外再增加长度,使其差分讯号达到等长的目的,如下图 :

前述说过,差分讯号不等长,会造成逻辑判断错误,而由[4]可知,间距不固定

对逻辑判断的影响,几乎是微乎其微。而阻抗方面,间距不固定虽然会有变化,但其变化通常在10%以内,只相当于一个过孔的影响。至于EMI 幅射干扰的增加,与抗干扰能力的下降,可在间距变化之处,用GND Fill 技巧,并多打过孔直接连到Main GND,以减少EMI 幅射干扰,以及被干扰的机会[24]。如前述,差分讯号最重要的就是要等长,因此若无法兼顾固定间距与等长,则需以等长为优先考虑。

17

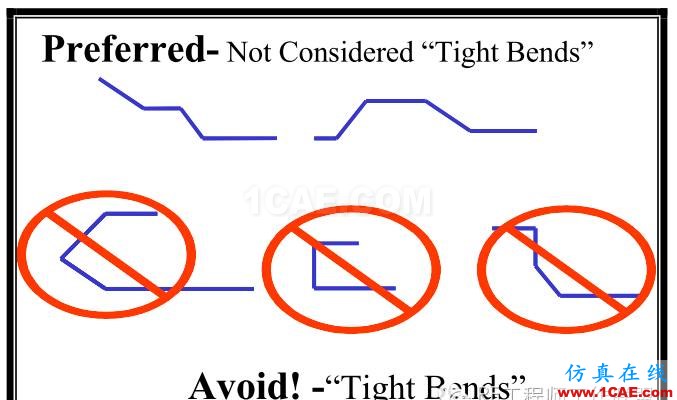

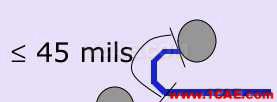

Bend

前述提到,差分走线有可能会因为转弯缘故,使得外侧走线会多出额外的长度,导致相位差,因而产生额外的共模噪声,因此最常见的方法便是再转一次弯,使原本内侧走线变成外侧走线,增加额外长度,来达到等长之效[1]。

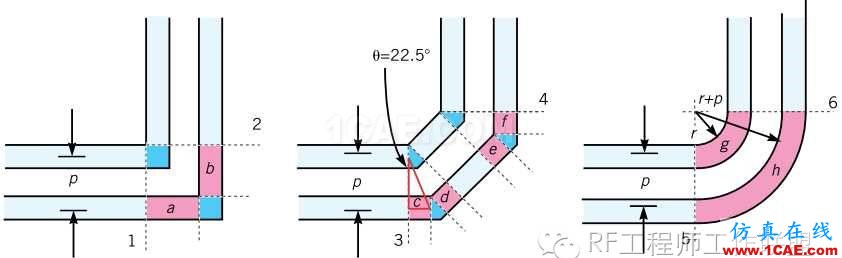

转角,会造成阻抗不连续,进而产生反射[42]。

18

另外,由[43]可知,理想的差分讯号,是不存在模态转换,但90 度转角会引起

相位差,导致部分讯号会差模转共模,产生额外的共模噪声,进而产生EMI 辐

射干扰。

19

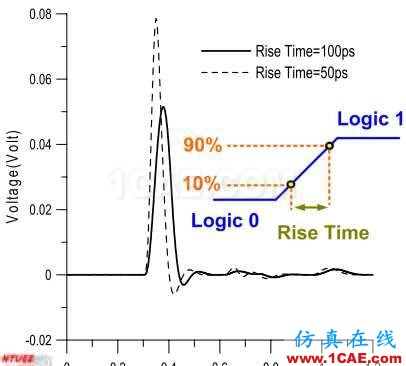

且由[42,44]可知,若上升时间越短,其90 度转角引起的共模噪声就越大。

而下图中的L 越长,其90 度转角引起的共模噪声也越大[42]。

20

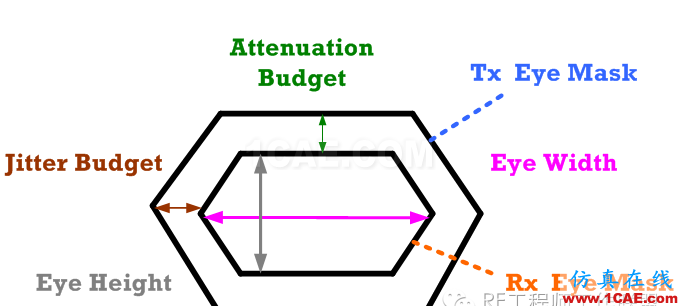

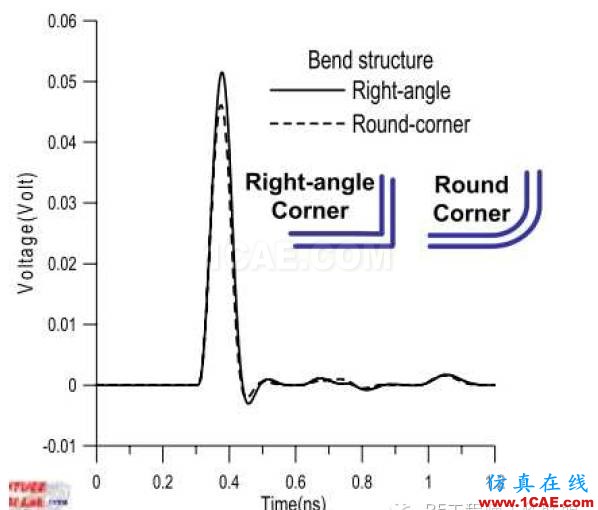

而若以眼图分析,由于90 度转角会阻抗不匹配,以及部分讯号会差模转共模,

因此会有损耗。且又因相位差而产生Jitter,换言之,90 度转角会使眼图的眼高

跟眼宽都变窄[12]。

因此在走线过程中,要极力避免90 度转角。

21

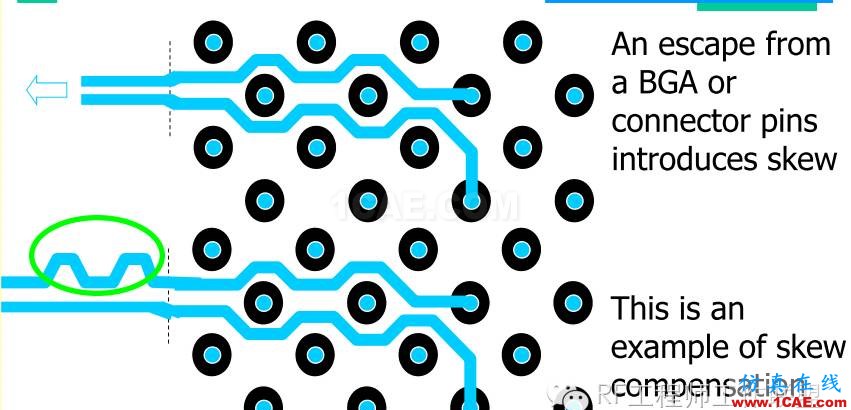

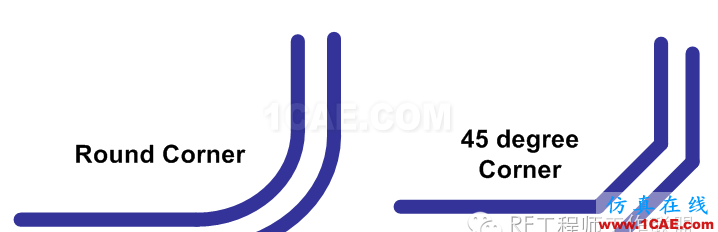

当然,实际的PCB 走线,不可能从头到尾都直线,没有转弯,换言之,转弯是

无可避免的,因此可利用45 度转角,以及圆滑转角,来取代90 转角。

或是因BGA的Pin 不对称,需靠转弯来达到等长之效时,可用下图方式达成41]。

22

由[44]可知,转角所造成的相位差,以90 度转角最大,45 度转角次之,圆滑转

角最小。

由此我们可知,只要是转角,就会有损耗,相位差跟共模噪声的产生,充其量只是程度多寡,理想上当然尽量避免使用,但如前述,实际的PCB 走线,转弯无可避免,因此只能靠45 度转角跟圆滑转角来将危害降低[44]。

23

由前述可知,差分讯号最重要的就是等长,虽然蛇状线与转角,都会有损耗,相位差跟共模噪声的产生,但却是为了确保等长,所不得不采取的措施。然而若以危害程度而言,蛇状线的危害比转角小一些,因此若空间许可,尽量用蛇状线代替转角,来达成等长的目的[41]。

24

Termination

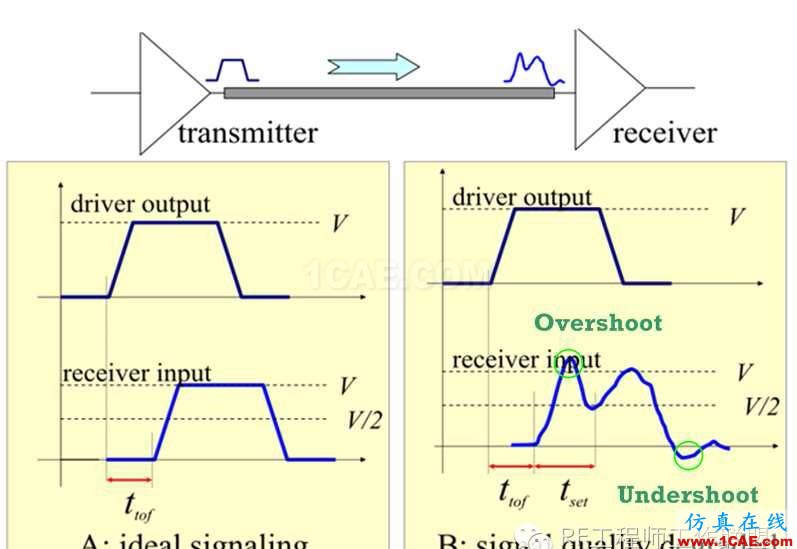

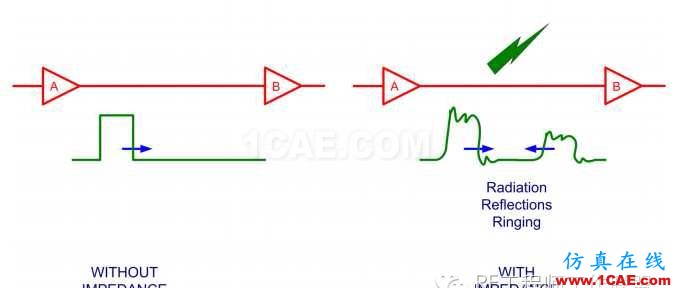

由[12]可知,数字讯号会因阻抗不匹配,而产生Overshoot 与Undershoot 现象,导致波形失真,以及使得系统的Noise Margin 变小,亦即系统抗噪声干扰的能力变弱。

同时也会产生EMI 辐射,产生噪声,造成干扰,因此需作阻抗匹配。

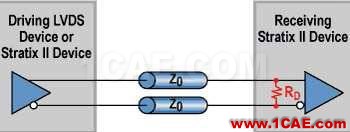

25

然而除了走线的阻抗控制,若要达到阻抗匹配,则需进一步仰赖匹配组件的辅助,有别于RF 走线,会利用电感与电容来作阻抗匹配[25],高速数字讯号,主要是利用电阻来作终端匹配[7,16],以降低反射。而差分讯号的终端电阻,一般都跨接在两信号之间,如下图[32] :

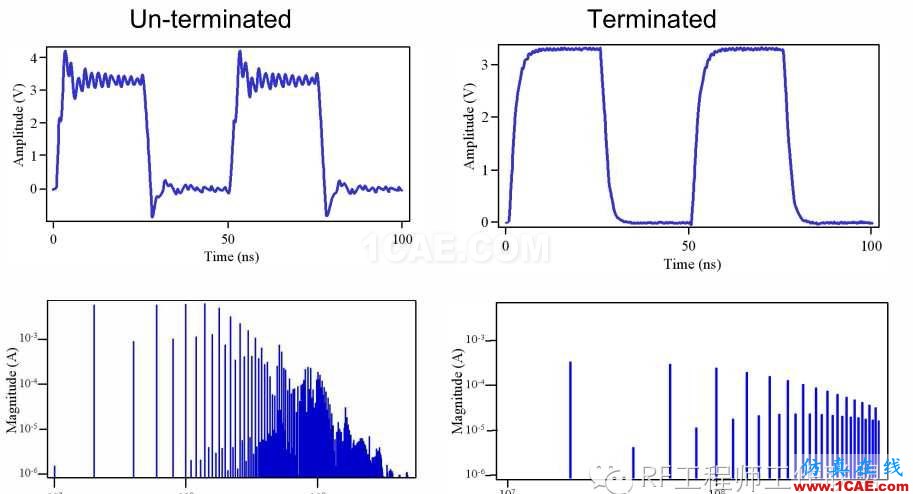

至于终端电阻的值,一般都在90 奥姆到130 奥姆之间。而做完终端匹配后,在

时域上,其信号Undershoot 与Overshoot 的现象大为改善,而在频域上,其噪

声成份也减少许多[12]。

26

EMI Filter

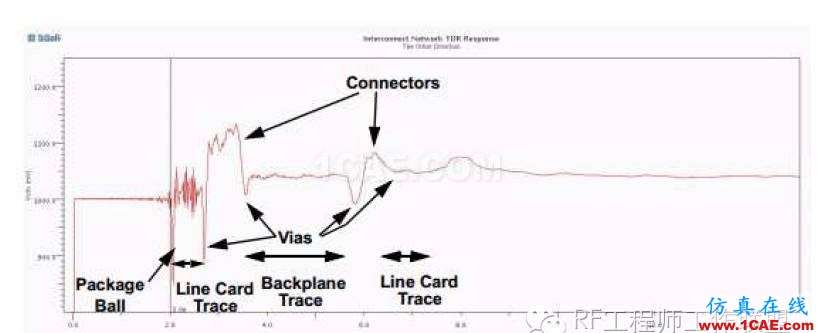

虽然对于高速数字的差分讯号号传递过程中,,我们利用了终端电阻来作匹配,然而实际上在信其阻抗很难从头到尾维持固定,例如会因为要避开过孔

,而导致阻抗不连续[33],

以及过孔跟连接器,所导致的阻抗不连续。

换言之,阻抗不连续的情况无可避免,因此高速数字讯号的EMI 辐射干扰,依然很大,反射是一定会有,在手机中,对于射频讯号,依然有很大危害,而导致致灵敏度下降。

27

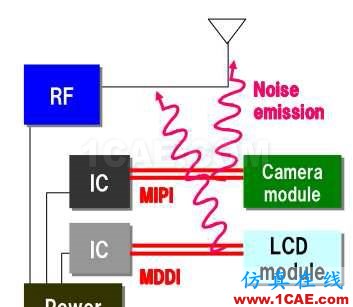

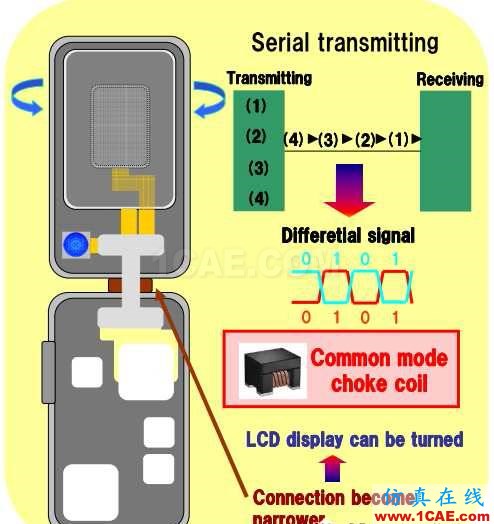

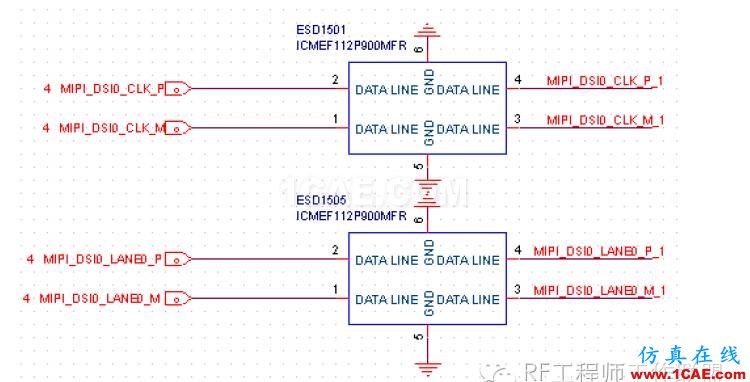

例如手机常用的MDDI,或MIPI 接口,有可能会透过天线,干扰接收讯号,导

,如下图[20] :

而以时域而言,其高频噪声会导致波形失真[22] :

因此必须进一步透过其他手段来抑制噪声,最常见的,就是EMI Filter,接下来

介绍其应用[12]。

28

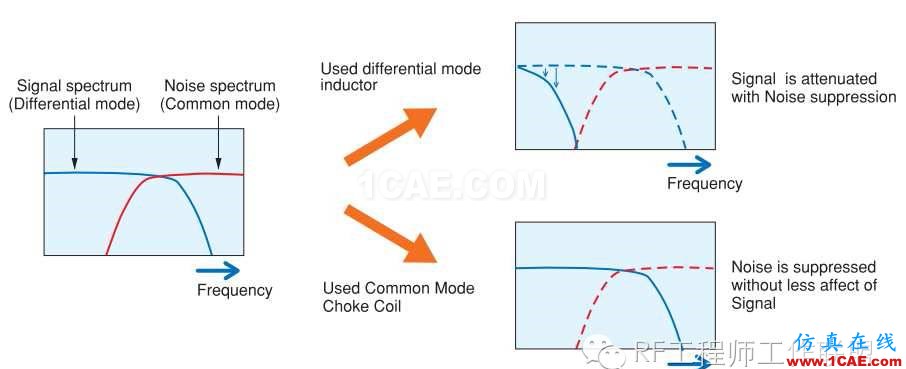

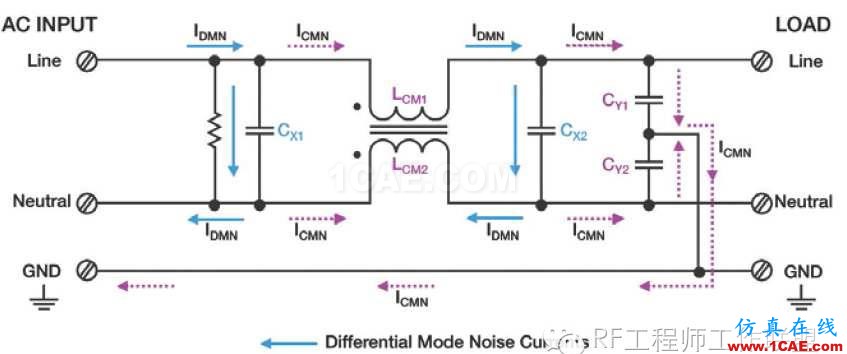

差分讯号的噪声,主要有分两种,共模与差模 :

29

然而,因为差分讯号也是采差模形式传递,若抑制其差模噪声,则可能会连其讯号也一并衰减,而抑制共模噪声,则对讯号几乎不会衰减,如下图 :

Choke,来抑制其共模噪声,其组成如下图,多半会以LC 电路构成。

30

以时域而言,添加了EMI Filter 后,其讯号波形便干净许多,降低了失真度,如

下图[22]。

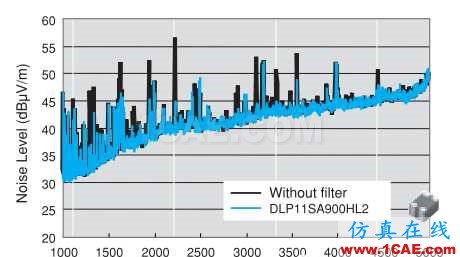

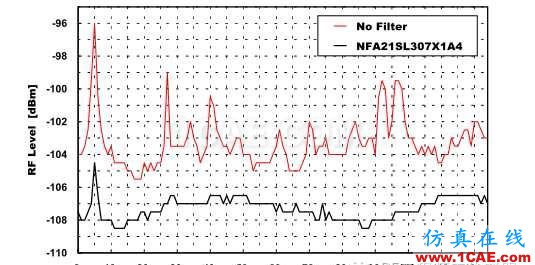

以频域而言,添加了EMI Filter 后,其Noise Floor 便明显下降许多,如下图[22]。

31

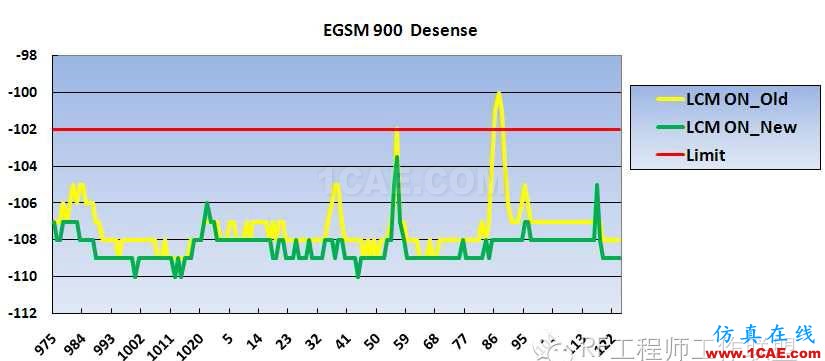

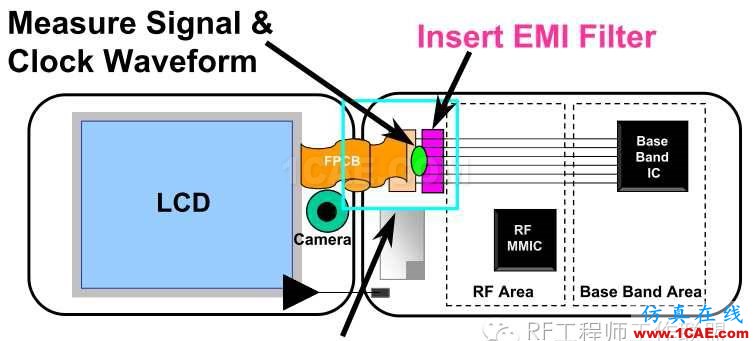

而以手机而言,当LCM On 时,会产生噪声使灵敏度下降,因此可以在其MIPI

讯号上,添加Common Mode Choke,如下图[12,20] :

32

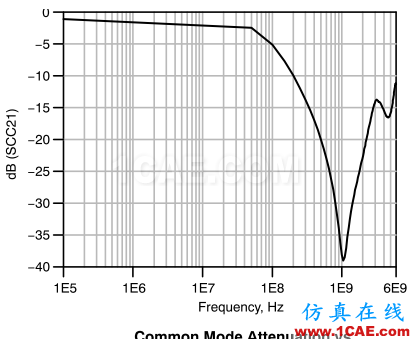

由前述知,差分讯号通常着重于共模噪声的抑制,因此在挑选Common Mode

Choke 时,尽量挑选共模噪声衰减量大一点的,如下图[12] :

下图黄色曲线,是原先的Common Mode Choke,可以看到仍有一些Channel 超标,而换了一个共模噪声衰减量较大的Common Mode Choke 后,大致上整体皆有所改善,且已无任何Channel 超标,如绿色曲线。

33

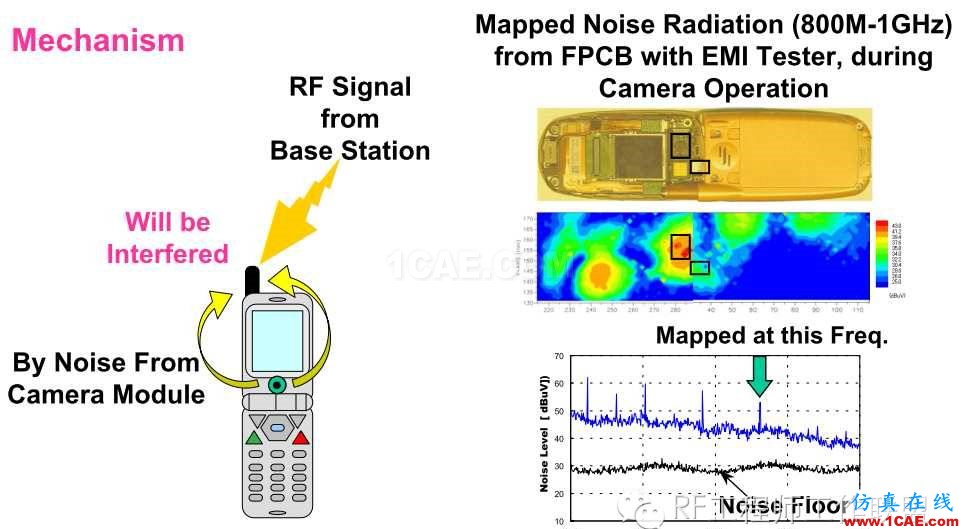

另外,当Camera On 时,也会产生噪声使灵敏度下降,如下图[21] :

也看出,摆放EMI Filter 后,其灵敏度确实改善[21]。

34

GND

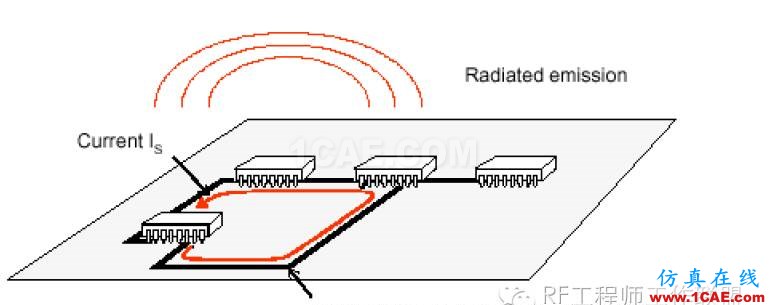

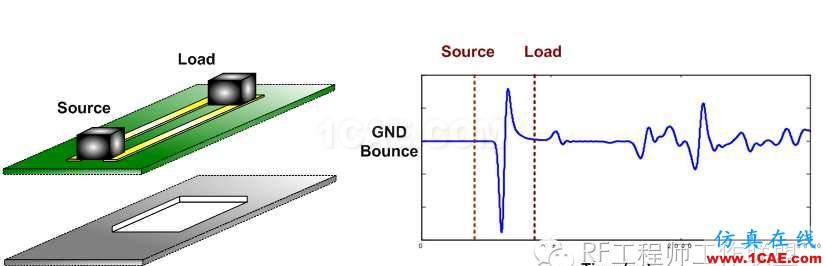

由[35]可知,任何讯号都会有回流电流,整体形成一个封闭回路,如下图 :

而电流流经封闭回路的磁场,会构成磁通量,其磁通量与电流的比值,便构成了电感,而电感又与感抗有关[12, 36]。

35

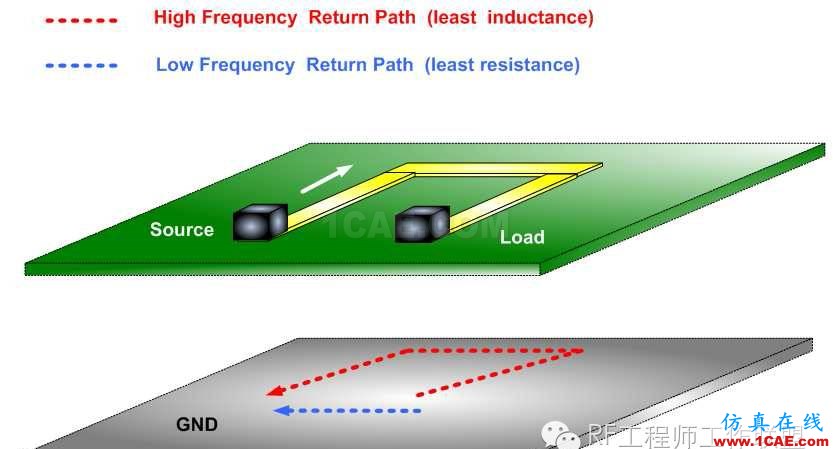

而由[38-39]可知,低频讯号的回流电流,会走最小电阻路径。而高频讯号的回

流电流,会走最小感抗路径,如下图[39] :

36

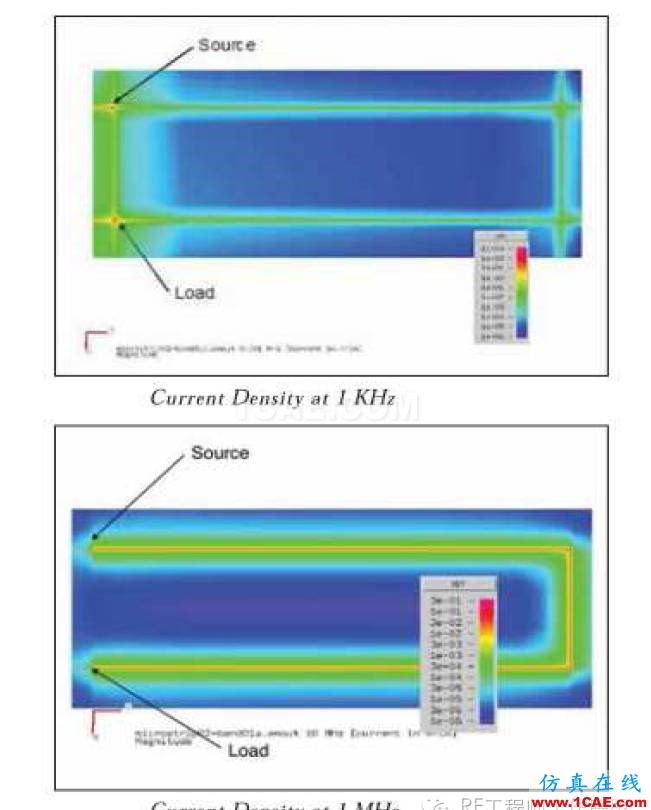

而由仿真结果也证实,当讯号为低频时,其回流电流只集中在Load 到Source

这段路径,但当讯号为高频时,其回流电流会集中在原路径下方[38]。

37

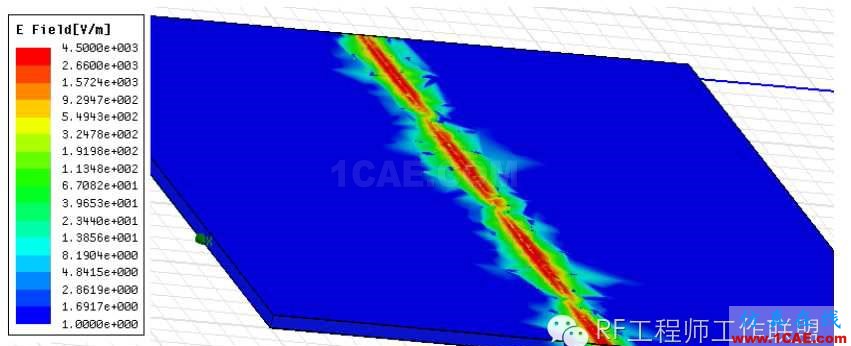

然而由下图可知,其差分讯号的回流电流,亦即GND Current,却几乎为零。那么,是否差分信号不需要GND 作为回流路径,直接以彼此为回流路径[1,5] ?

38

以Any Layer 的十层板为例,其讯号走线与GND 的距离为2.8 mil,就算下层挖

空,也只有5.6 mil[23]。

但由前述可知,表层走线若要达到100 奥姆,其间距差不多要10 mil,

39

而由[42]的模拟结果可知,瞬时时,其回流电流都集中在差分讯号原路径下方的

GND。

号在GND 的回流电流,亦即下图的i1 与i2,大小相等且方向相反,因此会相消,所以瞬时时,会有回流电流都集中在差分讯号原路径下方的GND,但稳态时,其GND Current,却几乎为零[4]。

40

由于单端讯号中,所谓的正电压或负电压,是跟GND ( 电位 = 0 ) 比较出来的,

因此若GND 的电位非恒为0,会有所谓的GND Bounce[12],而差分讯号中,所

谓的正电压或负电压,是彼此间比较出来的,如下图[17] :

实是存在于GND,换言之,GND 对于差分讯号,仍有一定的影响。由[44]可知,当差分讯号的GND 为一完整平面时,其Return Loss 至少有-20 dB,而Insertion Loss 也不大。

41

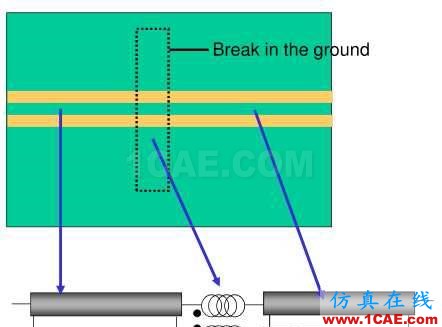

但当差分讯号的GND 有一开槽时,其Return Loss 几乎都不到-20 dB,而Insertion Loss 也明显变大许多,如下图[44] :

开槽时,会因为阻抗不连续,产生反射,因而Return Loss 变差。而由[44]可知,其开槽可等效于电感,由于电感会衰减高频讯号,故当差分讯号经过开槽时,其能量会衰减,因而Insertion Loss 变大。

42

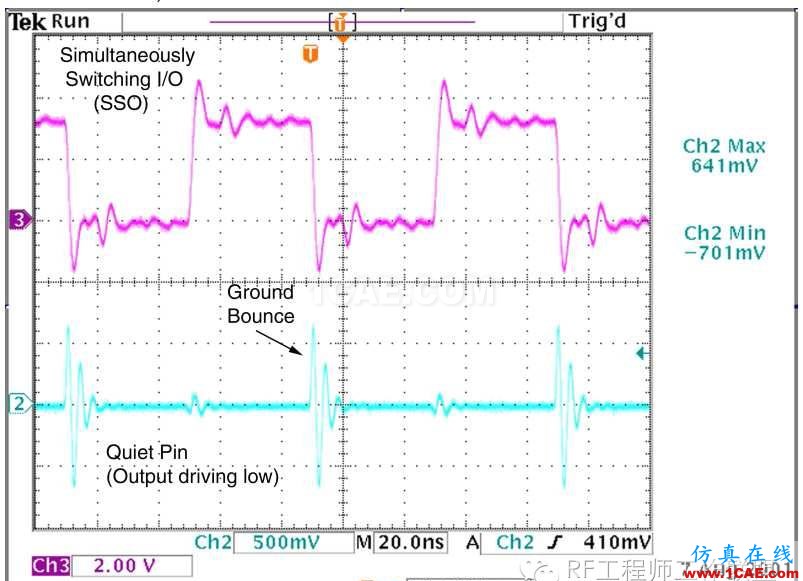

由[12]可知,GND Bounce,会使输出波形失真,以及影响邏辑运作的正确性,

进而使系统稳定度变差,如下图 :

讯号一般,GND 要维持完整性。

43

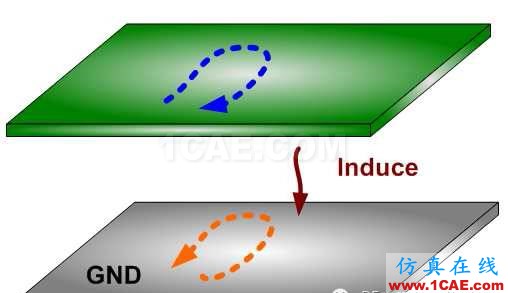

虽然差分讯号在GND 的回流电流会因相消而几乎为零,但会因Crosstalk,将能

量耦合过去,在其差分讯号正下方的GND,感应出一个方向相反,封闭回路的

感应电流[4]。

大差分讯号与GND 间的距离,来削弱感应电流的强度 ?

由前述可知,差分讯号的回流电流,确实是存在于GND,倘若将差分讯号与GND间的距离拉大,如此便等同于将差分讯号的回路面积扩大,势必会增加EMI 辐射干扰,这种作法弊大于利[5]。而由[35]可知,EMI 辐射干扰强度,与回路面积有关,同时感应电流的回路面积,亦等同于差分讯号的回路面积,因此,差分走线的长度要尽可能短,间距要尽可能小(但要符合阻抗控制),这样才能缩减差分走线与感应电流的回路面积[4],换言之,应该是透过缩减差分讯号回路面积的方式,来降低感应电流EMI 辐射干扰的强度,而不是直接将差分讯号与GND 间的距离拉大。

44

Reference

[1] Part 5 – BASIC DIFFERENTIAL SIGNALLING

[2] Differential Signaling, Ruey-Beei Wu

[3] The differential-signal advantage for communications system design

[4] DIFFERENTIAL TRACES AND IMPEDANCE

[5] PCB layout 中的走线策略

[6] LVDS 原理与应用简介

[7] LVDS 技术原理与设计

[8] Reducing EMI with differential signaling

[9] Design For EMI, INTEL

[10] Board Design Guidelines for LVDS Systems, Altera

[11] Field and Wave Electromagnetics, David K. Cheng

[12] 磁珠(Bead)_电感(L)_电阻(R)_电容(C)于噪声抑制上之剖析与探讨, 52RD

[13] LVDS Reduces EMI, FAIRCHILD

[14] 差分信号的介绍以及差分线在PCB 设计中的应用

[15] Differential Signaling, Lattice

[16] Introduction to IQ Signal, 52RD

[17] EMI countermeasure for Smartphone, TAIYO YUDEN

[18] The EMI Solution for Cellular Phone, Murata

[19] Electromagnetic Interference (EMI) 电磁干扰

[20] WCDMA 零中频发射机(TX)之调校指南与原理剖析, 52RD

[21] Common Mode Currents and Radiated Emissions from Differential

Signals in Multi--Board

[22] The Truth about Differential Pairs in High Speed PCBs

[23] 智能手机射频走线之阻抗控制, 52RD

45

[24] Layout Concern about Trace, Ground and Via, 52RD

[25] Passive Impedance Matching___实战大全, 52RD

[26] Termination Solutions in Stratix II Devices, ALTERA

[27] Breaking Up A Pair

[28] TDR: Reading the Tea Leaves

[29] EMC 基础知识, 华为

[30] Inductance 101: Modeling and Extraction

[31] 回流的基本概念

[32] Resistive vs. Inductive Return Current Paths

[33] Part 4 –PCB LAYOUT RULES FOR SIGNAL INTEGRITY

[34] DisplayPort PCB layout guidelines, NXP

[35] Board Design Guidelines for PCI Express Architecture

[36] Signal Integrity Issues for High-Speed Serial Differential Interconnects

[37] 高速連接器与线缆讯号完整性

[38] INTERCONNECT SIGNAL INTEGRITY, SAMTEC

[39] Your layout is skewed

[40] Layout & Routing: Front Panel Design

[41] PCI Express* Board Design Guidelines, INTEL

[42] Differential Lines, AWR

[43] High Speed PCB Layout Techniques

[44] 差分信号回流路径的全波电磁场解析

相关标签搜索:差分信号剖析与探讨 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析