ADC噪声系数 —— 一个经常被误解的参数

2017-04-03 by:CAE仿真在线 来源:互联网

现在,RF应用中会用到许多宽带运算放大器和ADC,这些器件的噪声系数因而变得重要起来。参考文献2讨论了确定运算放大器噪声系数的适用方法。我们不仅必须知道运算放大器的电压和电流噪声,而且应当知道确切的电路条件:闭环增益、增益设置电阻值、源电阻、带宽等。计算ADC的噪声系数则更具挑战性,大家很快就会明白此言不虚。

当RF工程师首次计算哪怕是最好的低噪声高速ADC的噪声系数时,结果也可能相对高于典型RF增益模块、低噪声放大器等器件的噪声系数。为了正确解读结果,需要了解ADC在信号链中的位置。因此,当处理ADC的噪声系数时,务必小心谨慎。

ADC噪声系数定义

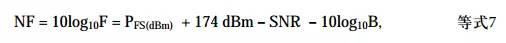

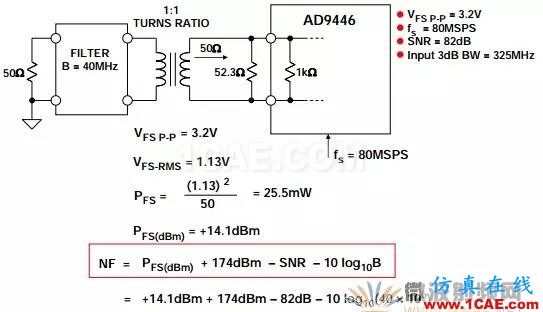

图1显示了用于定义ADC噪声系数的基本模型。噪声因数F指的是ADC的总有效输入噪声功率与源电阻单独引起的噪声功率之比。

由于阻抗匹配,因此可以用电压噪声的平方来代替噪声功率。噪声系数NF是用dB表示的噪声因数,NF = 10log10F。

图1:ADC的噪声系数:小心为妙!

该模型假设ADC的输入来自一个电阻为R的信号源,输入带宽以fs/2为限,输入端有一个噪声带宽为fs/2的滤波器。还可以进一步限制输入信号的带宽,产生过采样和处理增益,稍后将讨论这种情况。

该模型还假设ADC的输入阻抗等于源电阻。许多ADC具有高输入阻抗,因此该端接电阻可能位于ADC外部,或者与内部电阻并联使用,产生值为R的等效端接电阻。

ADC噪声系数推导过程

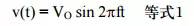

满量程输入功率是指峰峰值幅度恰好填满ADC输入范围的正弦波的功率。下式给出的满量程输入正弦波具有2VO的峰峰值幅度,对应于ADC的峰峰值输入范围:

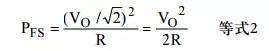

该正弦波的满量程功率为:

通常将此功率表示为dBm(以1 mW为基准):

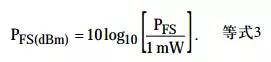

对滤波器的噪声带宽B需要加以进一步的讨论。非理想砖墙滤波器的噪声带宽指的是让相同的噪声功率通过时,理想砖墙滤波器所需的带宽。因此,一个滤波器的噪声带宽始终大于其3 dB带宽,二者之比取决于滤波器截止区的锐度。图2显示了最多5极点的巴特沃兹滤波器的噪声带宽与3 dB带宽的关系。注意:对于2极点,噪声带宽与3 dB带宽相差11%;超过2极点后,二者基本相等。

图2:巴特沃兹滤波器的噪声带宽与3dB带宽的关系

NF计算的第一步是根据ADC的SNR计算其有效输入噪声。ADC数据手册给出了不同输入频率下的SNR,确保使用与目标IF输入频率相对应的值。此外还应确保SNR数值中不包括基波信号的谐波,有些ADC数据手册可能将SINAD与SNR混为一谈。知道SNR后,就可以从下式开始计算等效输入均方根电压噪声:

这是在整个奈奎斯特带宽(DC至fs/2)测得的总有效输入均方根噪声电压,注意该噪声包括源电阻的噪声。

下一步是实际计算噪声系数。在图3中,注意源电阻引起的输入电压噪声量等于源电阻√(4kTBR)的电压噪声除以2,即√(kTBR),这是因为ADC输入端接电阻形成了一个2:1衰减器。

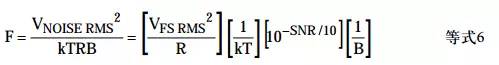

噪声因数F的表达式可以写为:

将F转化为dB并简化便可得到噪声系数:

其中,SNR的单位为dB,B的单位为Hz,T = 300 K,k = 1.38 × 10–23 J/K。

图3:根据SNR、采样速率和输入功率求得的ADC噪声系数

过采样和数字滤波会产生处理增益,从而降低噪声系数,这已在上文中说明。对于过采 样,信号带宽B低于f s /2。图4给出了校正因数,因而噪声系数的计算公式变为:

图4:过采样和处理增益对ADC噪声系数的影响

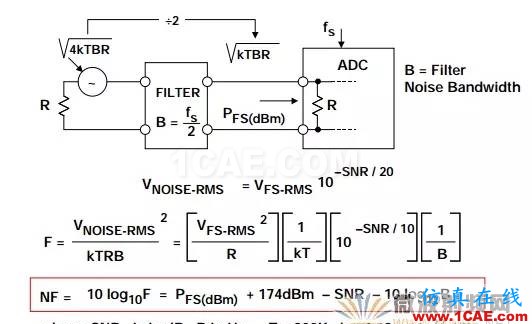

16位、80/100 MSPS ADC AD9446的计算示例

图5显示了16位、80/105 MSPS ADC AD9446的NF计算示例。一个52.3 Ω电阻与AD9446的1 kΩ输入阻抗并联,使得净输入阻抗等于50 Ω。ADC在奈奎斯特条件下工作,82 dB的SNR是利用上式8进行计算的基础,得到噪声系数为30.1 dB。

图5:16位80/100 MSPS ADC AD9446 在奈奎斯特条件下工作的噪声系数计算示例

利用RF变压器改善ADC噪声系数

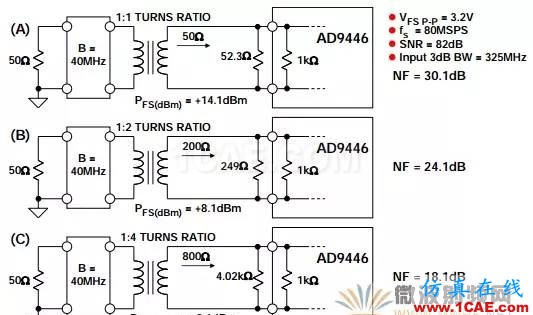

图6显示了如何利用具有电压增益的RF变压器来改善噪声系数。图6A中的变压器匝数比为1:1,噪声系数(来自图5)为30.1 dB。图6B中的变压器匝数比为1:2。249 Ω电阻与AD9446内部电阻并联,产生200 Ω的净输入阻抗。由于变压器的“无噪声”电压增益,噪声系数降低6 dB。

图6C中的变压器匝数比为1:4。AD9446输入端与一个4.02 kΩ电阻并联,使得净输入阻抗为800 Ω。噪声系数又降低6 dB。理论上,匝数比越高,则改善幅度越大,但由于带宽和失真限制,更高匝数比的变压器一般并不可行。

图6:利用RF变压器改善ADC整体噪声系数

级联噪声系数

即使采用匝数比为1:4的变压器,AD9446的整体噪声系数也有18.1 dB,按照RF标准,这一数值仍然较高。应当注意,AD9446 ADC的82 dB SNR代表了出色的噪声性能,系统应用的解决办法是在ADC之前提供低噪声高增益级。在一个典型接收机中,ADC之前至少有一个低噪声放大器(LNA)和混频级,它能提供足够高的信号增益,从而将ADC对系统整体噪声系数的影响降至最低。

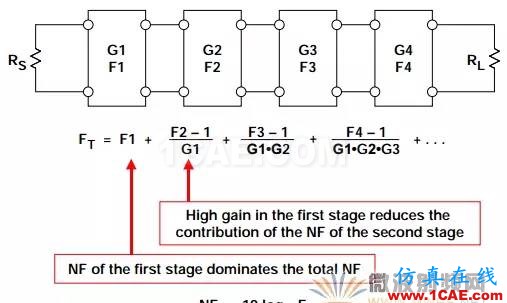

这可以通过图7来说明,其中显示了如何利用Friis等式来计算级联增益级的噪声因数。注意,第一级的高增益降低了第二级噪声因数的影响,因此第一级的噪声因数在整体噪声系数中占主导地位。

图7:利用Friis等式计算级联噪声系数

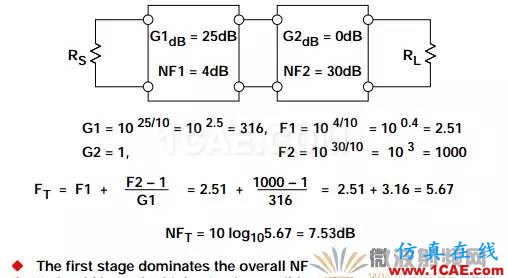

图8显示了置于一个相对较高NF级(30 dB)之前的一个高增益(25 dB)低噪声(NF = 4 dB)级的影响,第二级的噪声系数是高性能ADC的典型噪声系数。整体噪声系数为7.53 dB,仅比第一级噪声系数(4 dB)高3.53 dB。

图8:双级级联网络示例

结束语

应用噪声系数概念来表征宽带ADC时,必须特别小心,防止得出令人误解的结果。试图简单地通过改变等式中的值来降低噪声系数可能会适得其反,导致电路总噪声提高。

例如,根据以上等式,NF随着源电阻的增加而降低,但增加源电阻会提高电路噪声。另一个例子与ADC的输入带宽B有关。根据等式,提高B会降低NF,但这显然是相互矛盾的,因为提高ADC输入带宽实际上会提高有效输入噪声。在以上两个例子中,电路总噪声提高,但NF降低。NF降低的原因是源电阻或带宽提高时,信号源噪声占总噪声中的较大部分。然而,总噪声保持相对稳定,因为ADC引起的噪声远大于信号源噪声。因此,根据等式,NF降低,但实际电路噪声提高。

有鉴于此,当处理ADC时,必须小心处理NF。利用本文中的等式可以获得有效的结果,但如果不全面理解其中涉及到的噪声原理,这些等式可能会令人误解。

从孤立的角度看,即使是低噪声ADC,其噪声系数也会相对高于LNA或混频器等其它RF器件。然而,在实际的系统应用中,ADC前方至少会放置一个低噪声增益模块,根据Friis等式(见图8),它会把ADC的总噪声贡献降至非常低的水平。

作者:Walt Kester

参考文献

1. Kevin McClaning and Tom Vito, Radio Receiver Design, Noble Publishing, 2000, ISBN1-88-4932-07-X.

2. Walter G. Jung, Op Amp Applications, Analog Devices, 2002, ISBN 0-916550-26-5,Also available as Op Amp Applications Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5.

3. Walt Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3,Also available as The Data Conversion Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0.

4. Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1.Also available as Linear Circuit Design Handbook, Elsevier-Newnes, 2008, ISBN-10:0750687037, ISBN-13: 978-0750687034.

相关标签搜索:ADC噪声系数 —— 一个经常被误解的参数 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析