ADS高速电路设计/信号完整性仿真专题之串扰

2017-04-03 by:CAE仿真在线 来源:互联网

编者注:高速电路设计是当下电路发展的趋势,那么仿真对于高速电路设计而言是不可或缺的一种手段。15年的时候开始给大家分享一些软件使用方法,接下来结合一些实际和热点问题给小伙伴们继续分享。大家对于一些比较关注的话题或者困惑的问题,也可以留言,进一步交流。

鉴于国内外的很多ADS的资料都是微波射频领域的,接下来,会慢慢的分享一些ADS在信号完整性领域经常使用的小功能和技巧。

今天给大家介绍使用ADS进行串扰的仿真。串扰在高速电路设计中被提及非常多的一个话题,串扰要么不产生问题,要产生了问题就很难解决,所以建议大家在做设计之前做一些串扰仿真,通过仿真了解各种因素对串扰产生的影响,这样比大家死机硬背一些教条主义经验要好的多。

关于串扰的理论,大家可以参照Eric的《信号完整性分析》等书籍。

小伙伴们可能都知道,串扰与很多因素有关系,如传输线之间的耦合长度、传输信号的上升时间、传输线之间的间距等等。这里就以这三个因素为例,对串扰做一些定性的分析:

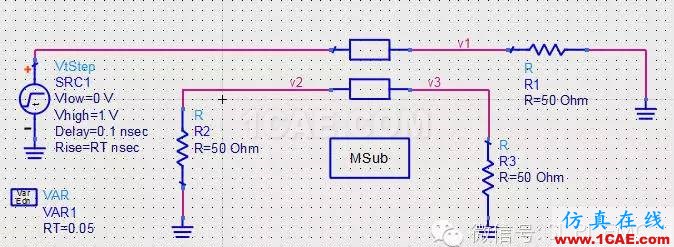

在ADS中搭建仿真的拓扑结构,这一点非常的重要,因为要是拓扑结构搭建都有问题,那么就使得仿真结果变得不可分析,所以,在如下的仿真中,都尽量以单一变量做仿真实验。

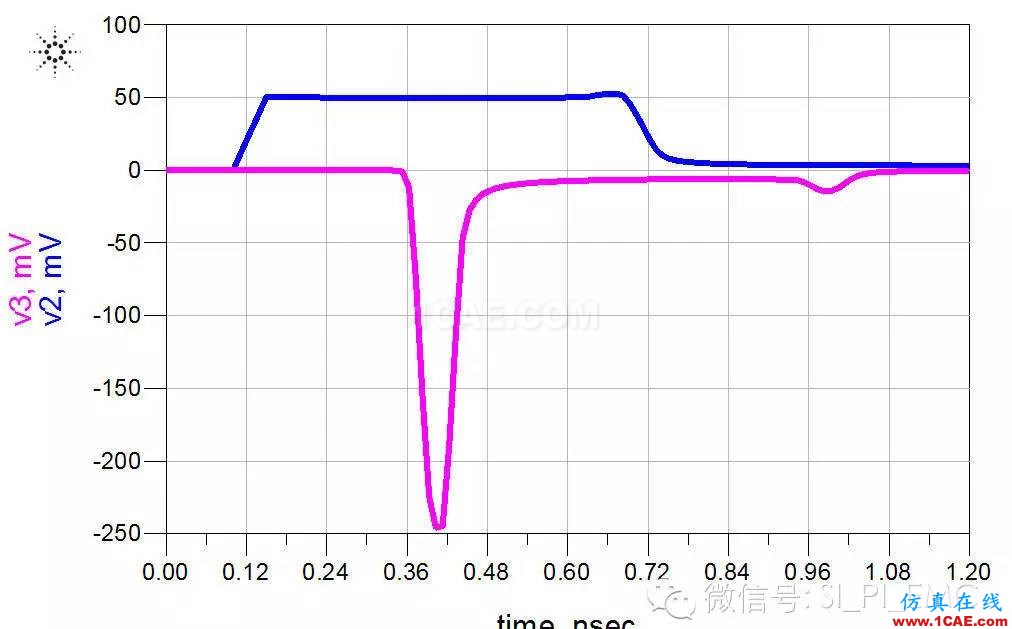

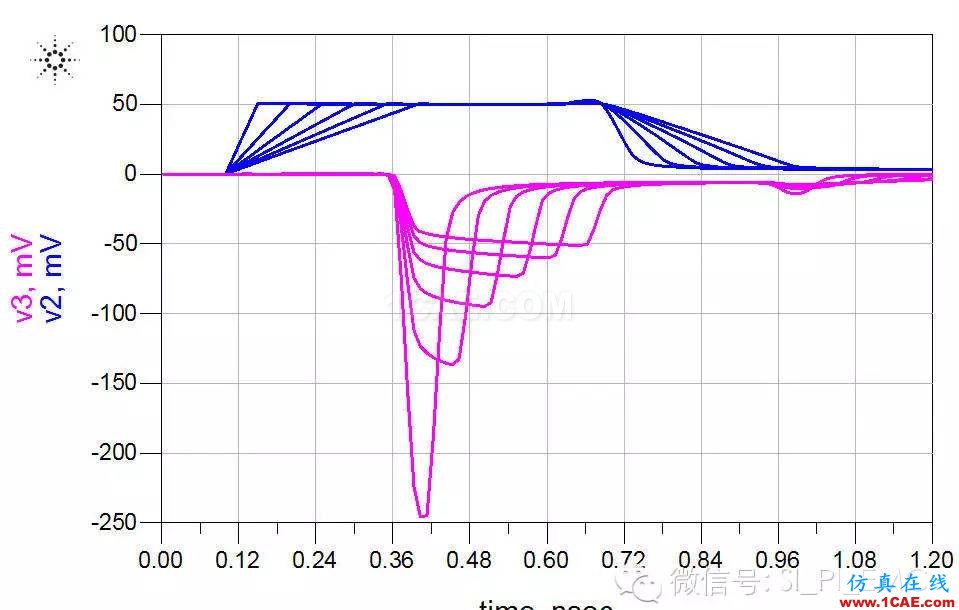

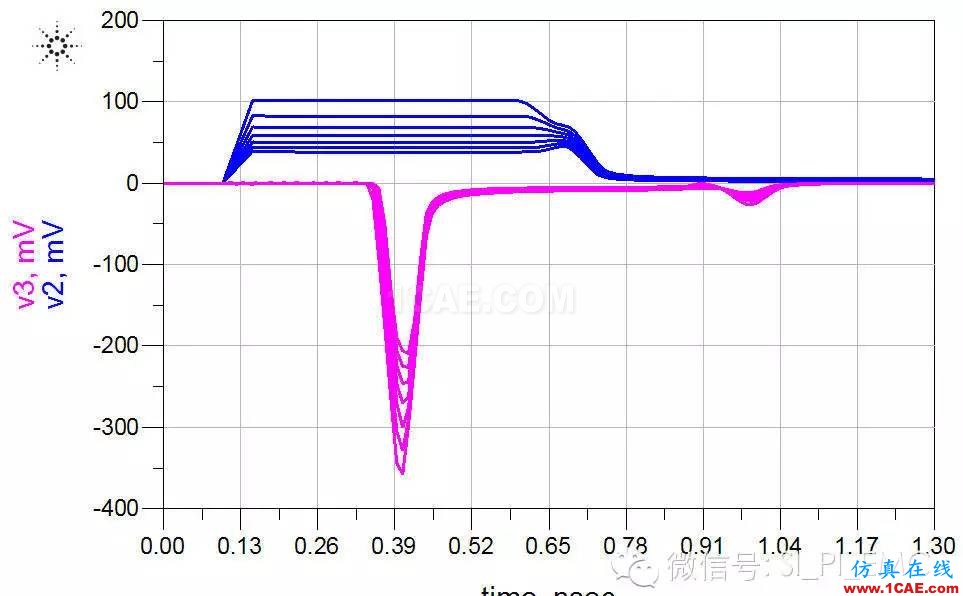

得到的串扰结果如下(蓝色为近端串扰NEXT,粉色为远端串扰FEXT):

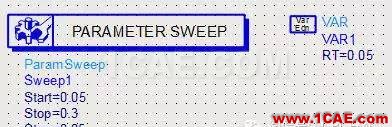

1、上升时间:考察上升时间时,其他的参数都不变,只改变上升时间的变量,所以需要加入变化参量和扫描参数,如下所示:

上升时间从50ps开始,300ns截止,每隔50ps仿真一次,得到的仿真结果如下:

结论:随着上升时间变长,其远端串扰变小,饱和长度变长。

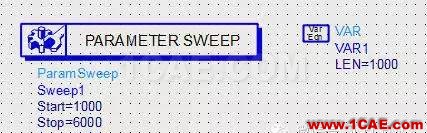

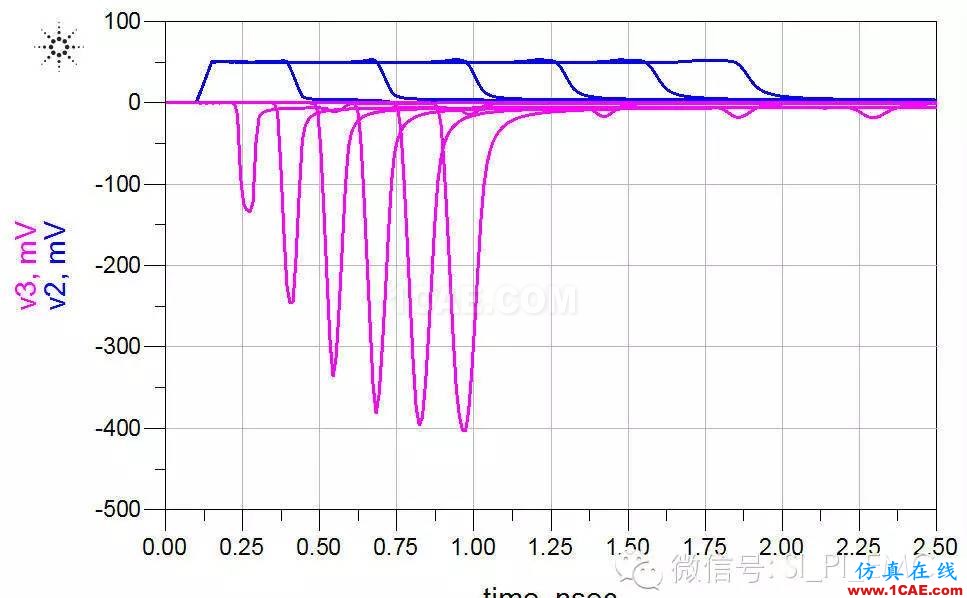

2、耦合长度:改变耦合长度,其他参数保持不变。长度由1inch开始,截止到6inch,每隔1inch仿真一次,变化参量和扫描参数如下:

得到的仿真结果如下:

结论: 随着耦合长度的增加,其远端串扰一直在增加,在1inch之前就已经达到饱和长度,所以在此实验中,1inch之后增加耦合长度对近端串扰没有影响。

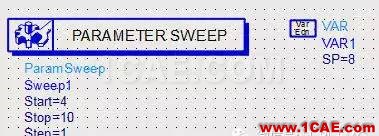

3、传输线间距:改变传输线间距,其他参数保持不变。间距由4mil开始,截止到10mil,每隔1mil仿真一次,变化参量和扫描参数如下:

得到的仿真结果如下:

结论:由仿真结果可知,其间距越大,其近端串扰和远端串扰都会变小。

以上这些仿真例子只是抛砖引玉,大家可以进一步的仿真对比微带线与带状线的串扰、仿真对比包地对串扰的影响、传输线到参考层的距离等等。

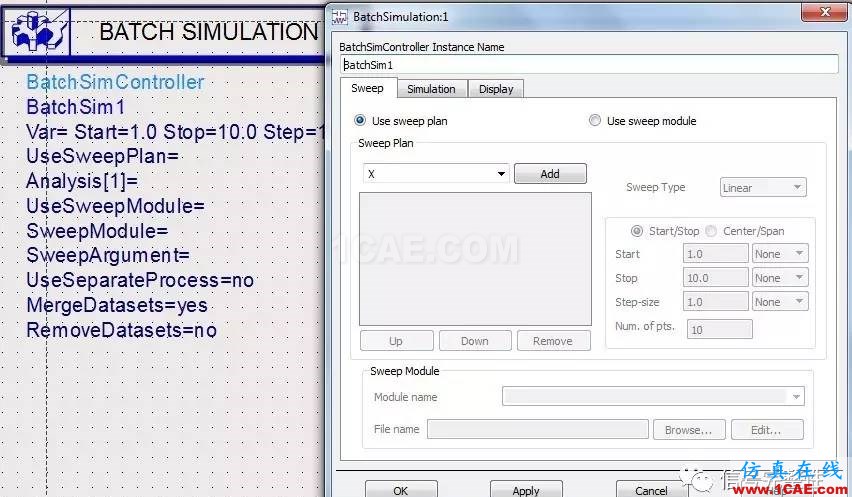

在这些实验中,讲解了ADS参数扫描(Sweep)的仿真,还可以对多个参数同时进行扫描,即使用BatchSimulation功能:

其实大家在做硬件电路设计很多时候都会死记硬背很多公式和结论,比如满足3W规则,高速传输线链路上不能加Via,等等。记得住也记得对当然很好,但是如果记不住也不知道对不对,还不如使用一些简单的仿真软件对相关的问题进行仿真,就可以得到很多实用的经验和结论,那么在设计的时候就可以做到有的放矢。

转自公众号:信号完整性(SI_PI_EMC)

相关标签搜索:ADS高速电路设计/信号完整性仿真专题之串扰 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析