基于ANSYS的ADC无杂散动态范围指标仿真分析

2017-04-03 by:CAE仿真在线 来源:互联网

概述:

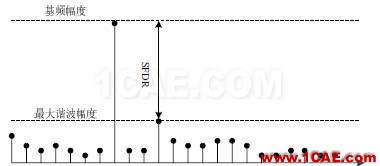

ADC 的无杂散动态范围(Spurious-free Dynamic Range,SFDR)是指载波频率(基频)的RMS 幅度与最大噪声成分或者谐波成分的RMS 之比。SFDR 通常以dBc(相对于载波频率幅度)或dBFS(相对于ADC 的满量程范围)来表示。下图给出了SFDR 示意图:

仿真思路:

为了更直观的展示HFSS在ADC无杂散动态范围设计优化方面的应用,这里以一个ADC的PCB板布线为例,介绍ANSYS在PCB板上ADC模拟输入信号无杂散动态范围性能优化方面的仿真分析方法。

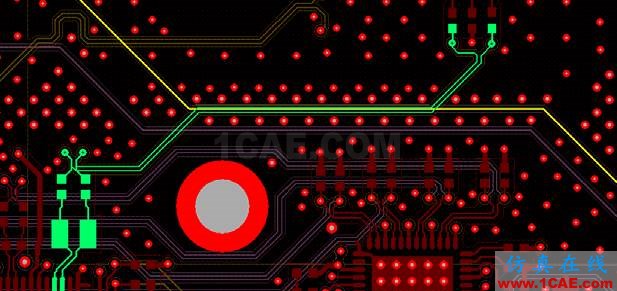

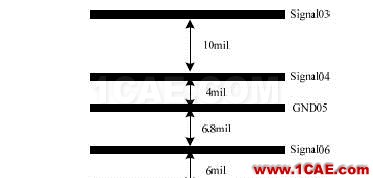

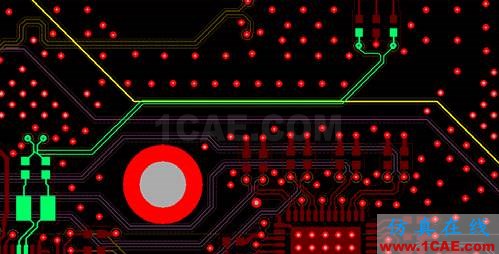

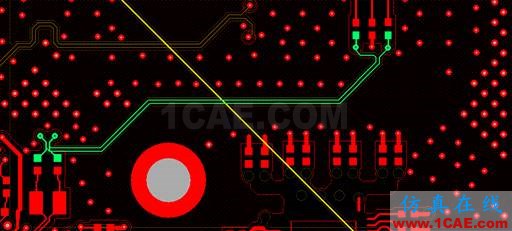

该ADC的PCB布线图和层叠图如下。(图中绿色为L4层的ADC模拟输入走线,黄色为L6层的时钟信号走线,两者平行走线长度约为10mm)

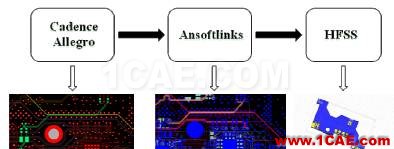

1)借助Ansoftlinks将PCB结构从PCB布线工具中导出到HFSS软件中,提取6端口S参数,流程如下图:

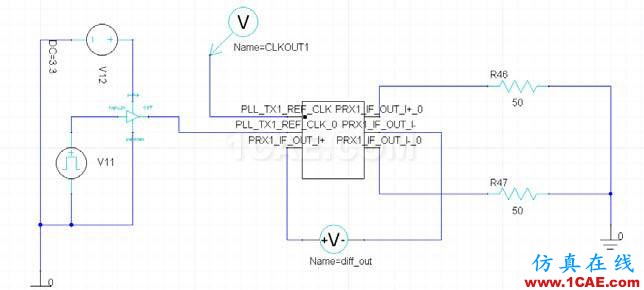

2)在 Ansoft Designer 中搭建仿真电路,包括时钟激励源V11(频率为61.44MHz,幅度为3.3V),本振时钟驱动BUFFER,然后调入1)中提取的6 端口S 参数,将本振时钟驱动BUFFER 的输出端接入S 参数中本振时钟的输入端口,输出端口接一个观察探针,并将模拟通道输出端进行50 欧姆端接匹配,通过输入端的差分探针观察后向串扰时域波形和频域频谱,如下图:

3)对 PCB 上的走线进行调整,第一种调整方案是删除模拟输入信号和本振时钟信号平行走线段的地过孔;第二种方案是保持地回流过孔不变,模拟信号表层走线不打换层过孔;第三种方案是保持走线层和地回流过孔不变,拉大时钟信号线与模拟信号换层过孔间的距离。对这三种情况分别进行1)、2)步骤仿真,将仿真结果与原始走线情况下的仿真结果进行对比,以确认主要耦合路径。

仿真结果:

1)原始走线

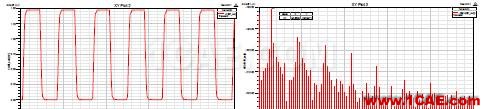

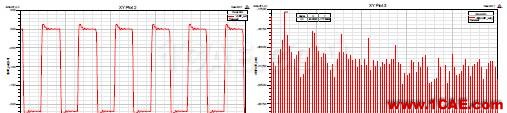

模拟信号输入端时域信号波形以及信号频谱如下图:

从串扰的时域波形可以看出,串扰的幅度非常小,只有nV 级,这符合我们对走线叠层的分析;从模拟信号输出端信号频谱上可以看到主要干扰频率为60MHz,幅度为-155.5072dB。

2)删除平行走线的地过孔

首先假设模拟信号与时钟信号平行走线段地密集地过孔是串扰耦合的路径,在PCB上将这一段的地过孔全部删除,如下图所示:

此时,模拟信号输入端时域信号波形以及信号频谱如下图所示:

从频谱上看,串扰的主频为60MHz,而幅度为-156.5310dB,与未删过孔前的-155.507dB 相比下降1 个dB 左右。仿真结果表明平行走线地过孔不是主要的耦合路径。

3)模拟输入信号改为表层走线

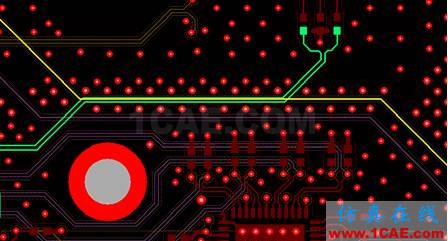

其次,假设串扰从模拟信号的换层过孔处耦合进入模拟通道,为此将模拟输入信号改为表层走模拟输入信号,如下图所示。

此时,模拟信号输入端时域信号波形以及信号频谱如下图所示:

从频谱上看,串扰的主频为60MHz,而幅度为-180.9671dB,与打孔换层情况下的-155.507dB 相比下降25.46 个dB。该仿真结果表明ADC 模拟信号输入信号换层过孔可能是主要的耦合路径。

4)拉大时钟信号与模拟输入信号换层过孔的距离

为了进一步验证模拟信号换层过孔的影响,我们在PCB上拉大时钟信号与换层过孔的距离,如下图所示:

此时,模拟信号输入端时域信号波形以及信号频谱如下图所示:

从频谱上看,串扰的主频为60MHz,而幅度为-177.3869dB,与未拉大距离之前相比下降了21.8797 个dB,相对下降幅度较大。板上时钟信号线与模拟输入信号换层过孔距离较近(4.3mm 左右),将该距离拉大之后(10mm 左右)串扰主频幅度下降21.8 个dB 左右,说明模拟信号的换层过孔是主要的串扰耦合路径。

通过仿真对比我们发现,模拟输入信号的换层过孔为时钟信号噪声的主要耦合路径。需要将时钟信号与模拟信号的换层过孔进行充分的隔离,如采用拉大两者之间的距离、模拟信号表层走线等方式。

结论:

Ansoft 系列仿真软件间良好的接口性能,使得产品的PCB结构能容易导入到仿真软件中进行协同仿真。利用高精度三维电磁场仿真软件HFSS 进行S 参数提取保证了仿真结果的可靠性。

相关标签搜索:基于ANSYS的ADC无杂散动态范围指标仿真分析 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析