高速差分过孔之间的串扰分析

2017-04-14 by:CAE仿真在线 来源:互联网

在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

高速差分过孔间的串扰

对于板厚较厚的PCB来说,板厚有可能达到2.4mm或者3mm。以3mm的单板为例,此时一个通孔在PCB上Z方向的长度可以达到将近118mil。如果PCB上有0.8mmpitch的BGA的话,BGA器件的扇出过孔间距只有大约31.5mil。

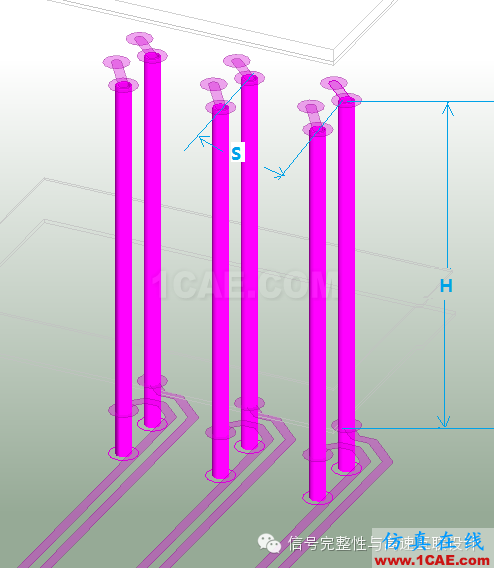

如图1所示,两对相邻差分过孔之间Z方向的并行长度H大于100mil,而两对差分过孔在水平方向的间距S=31.5mil。在过孔之间Z方向的并行距离远大于水平方向的间距时,就要考虑高速信号差分过孔之间的串扰问题。顺便提一下,高速PCB设计的时候应该尽可能最小化过孔stub的长度,以减少对信号的影响。如下图所1示,靠近Bottom层走线这样Stub会比较短。或者可以采用背钻的方式。

图1:高速差分过孔产生串扰的情况(H>100mil, S=31.5mil )

差分过孔间串扰的仿真分析

下面是对一个板厚为3mm,0.8mmBGA扇出过孔pitch为31.5mil,过孔并行距离H=112mil的设计实例进行的仿真。

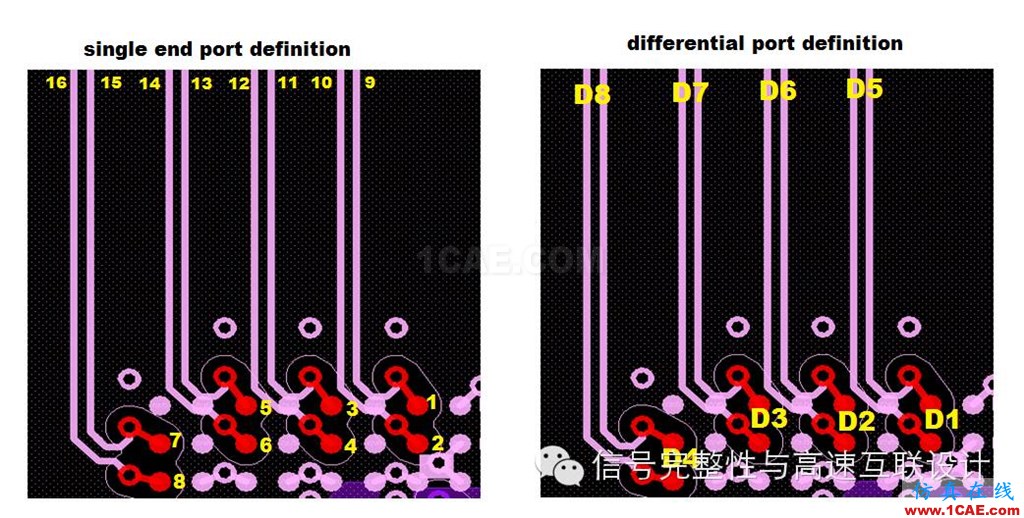

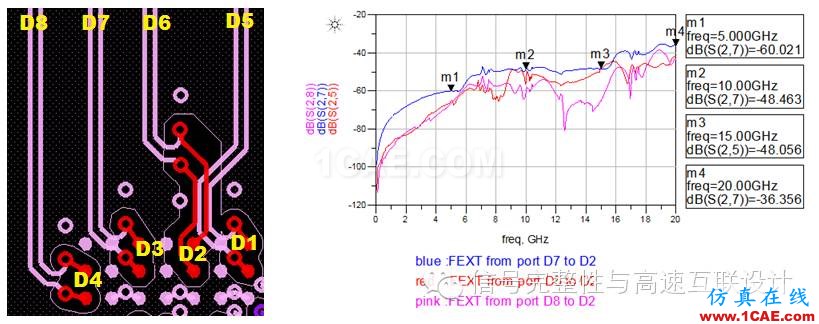

如图2所示,我们根据走线将4对差分对定义成8个差分端口。

图2:串扰仿真端口定义

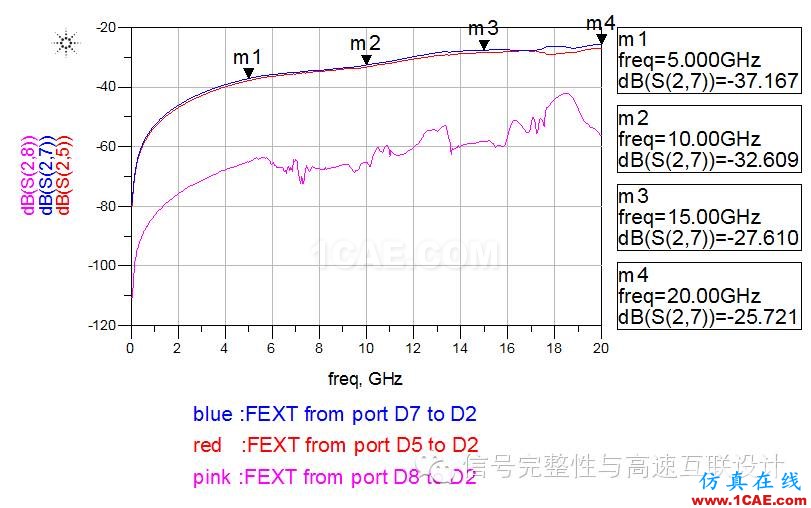

假设差分端口D1—D4是芯片的接收端,我们通过观察D5、D7、D8端口对D2端口的远端串扰来分析相邻通道的串扰情况。由图3所示的结果我们可以看到距离较近的两个通道,通道间的远端串扰可以达到-37dB@5GHz和-32dB@10GHz,需要进一步优化设计来减小串扰。

图3:差分对间的串扰仿真结果

也许读到这里您会产生疑问:如何判定是差分过孔引起的串扰而不是差分走线引起的串扰呢?

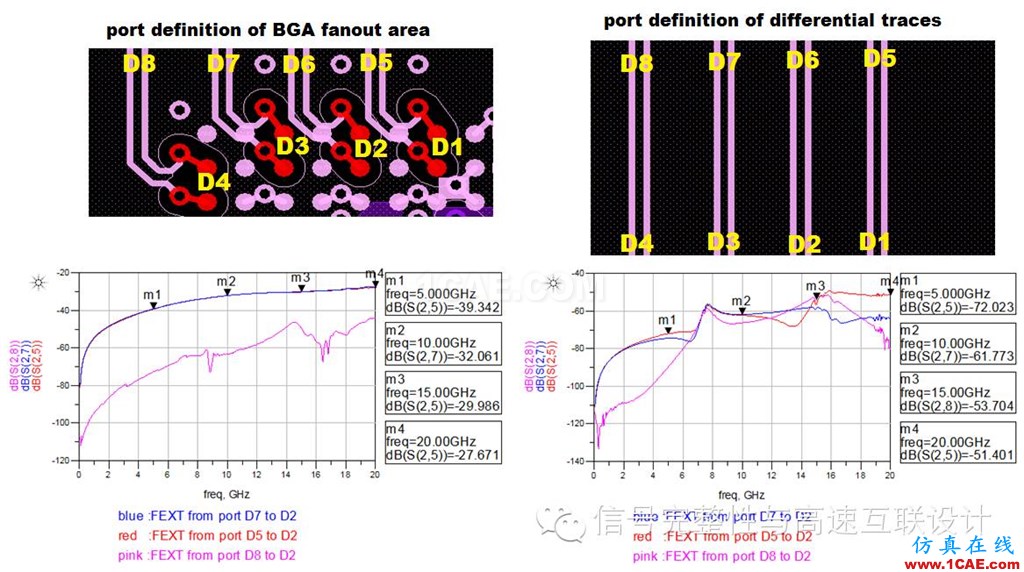

为了说明这个问题,我们将上述的实例分成BGA扇出区域和差分走线两部分分别进行仿真。仿真结果如图4所示:

图4:BGA扇出区域和差分走线串扰仿真结果

从图4右侧的仿真结果可以看出差分走线间的串扰都在-50dB以下,在10GHz频段下甚至达到了 -60dB以下。而BGA扇出区域的串扰和原来整体仿真的串扰数值比较接近。从图4中的仿真结果我们可以得出在上述实例中差分过孔间的串扰起主要作用。

差分过孔间串扰的优化

了解了此类问题产生串扰的根源,优化差分过孔之间串扰的方法就比较明确了。增加差分过孔之间的间距是简单易行并且十分有效的方法。我们在实例原设计的基础上将差分过孔位置进行了优化,使得每对差分过孔之间的间距大于75mil。从图5所示的仿真结果以及表1的数据对比可以看出,优化后的远端串扰比原设计在15GHz频带内有15~20dB的改善,在15~20GHz频带内有10dB的改善。

图5:优化差分过孔间距后串扰仿真结果

|

|

5G |

10G |

15G |

20G |

|

优化前串扰(dB) |

-37.167 |

-32.609 |

-27.61 |

-25.721 |

|

优化后串扰(dB) |

-60.021 |

-48.463 |

-48.056 |

-36.356 |

|

优化效果(dB) |

22.854 |

15.854 |

20.446 |

10.635 |

表1:优化差分过孔间距前后串扰仿真数据对比

相关标签搜索:高速差分过孔之间的串扰分析 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析