由驱动能力引起的信号完整性案例解读

2017-05-21 by:CAE仿真在线 来源:互联网

由驱动能力引起的信号完整性案例解读

一个高速器件放在一堆低速电路中,其信号完整性的问题会比较突出;而一个低速器件放在一堆高速电路中, 其驱动能力的问题就会显得比较突出。 为什么, 请看 “案例: 驱动能力不足造成的时序错误”。另外, 也有器件选型和匹配方案不当带来的驱动能力问题, 当器件驱动的信号沿大大超出其翻转速率时,所带来的问题除了信号沿变缓外,还可能造成信号摆幅变小,阈值电平违规等。详见“案例:错误的设计带来的驱动能力问题”。

1 案例:驱动能力不足造成的时序错误

一块单板,设计有 DSP 和 FPGA。 FPGA 的加载模式设置为 Slave Serial 模式,上电时 DSP 从外挂FLASH 中读取 FPGA 的 bit 文件,并加载 FPGA。发现的故障是: FPGA 加载有一定失败的概率。

示波器监测 FPGA 的 INIT_B 信号,发现该信号在加载数据过程中会拉低且无法恢复。(正常流程该信号只在加载初始化时输出低脉冲)。 INIT_B 信号在加载数据过程中拉低,表示 FPGA 检测到了数据CRC 出错。分别导出 FPGA 加载成功和加载失败两种情况下, DSP 从 FLASH 中读到 SDRAM 中的 bit文件,并进行比较,发现二者有少量字节有差异。由此判断, DSP 在将 FPGA 加载数据从 FLASH 向SDRAM 搬移的过程中,出现了误码。 DSP 本身的程序运行依赖于 SDRAM,如果 SDRAM 访问有问题,DSP 应该容易跑飞。鉴于故障复现时未发生 DSP 跑飞的现象,我们把排查的重点放在读 FLASH 的过程上。

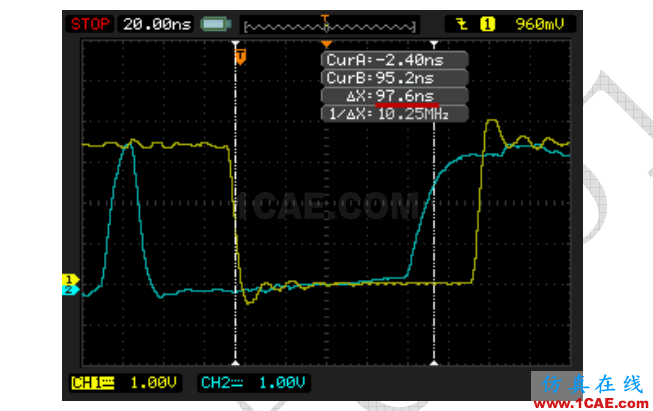

硬件电路上, FLASH 挂在 DSP 的本地总线上,作为异步存储器被 DSP 访问, FLASH 的标称访问时间是 90ns,依此来检查 DSP 对 FLASH 空间的时序配置,读数时的建立保持时间应该都是足够的。但经过实测发现,建立时间的时序裕量为负值。究其因,是因为 FLASH 输出的信号沿太缓,几乎达到了 20ns,如图 14通道二波形。这样缓的信号沿,直接导致了 FLASH 访问时间的延长,超过了 97ns。

找到问题根源后,根据测量结果修改 DSP 对 FLASH 空间的异步时序配置,以保证足够的裕量,问题便迎刃而解了。在一个总线频率超过 50MHz 的处理器系统中, FLASH 相对来说属于较低速的器件,其管脚驱动能力也较弱。如果处理器总线上挂的负载比较多,由于容性负载的增大, FLASH 驱动总线时,其输出信号沿势必会变得更缓。而信号沿变缓带来的额外延时,往往容易被忽略。设计者在处理类似的接口时,应该充分考虑各种可能给时序带来冲击的参数,以保证接口的稳定可靠。

2 案例:错误的设计带来的驱动能力问题

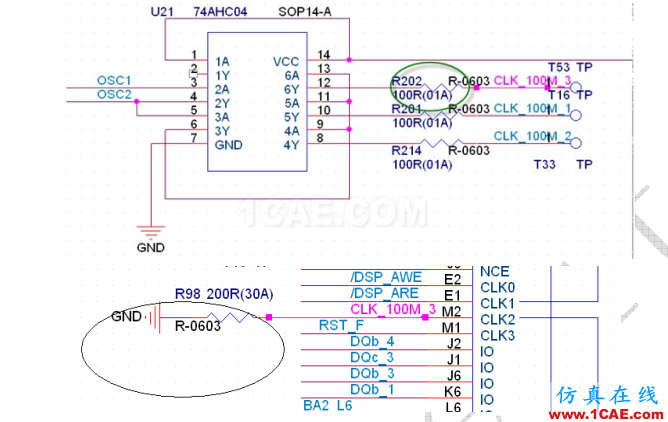

一个 100MHz 时钟,由晶体驱动反相器 74AHC04 产生,作为 FPGA 的时钟全局时钟使用。 FPGA的管脚电平设置为 LVTTL33。电路工作过程中,发现 FPGA 工作紊乱,将时钟引出测量,时有时无,很不稳定。测量 100MHz 时钟输入,发现高电平只有 1.5V 左右。该电平无法保证被 FPGA 正确识别为高。这是一个典型的工程师经验不足造成的原始设计缺陷。分析这个 100MHz 时钟的原理图 (如图 15),1 分钟内发现三个问题:1.最大的问题,反相器的选型: 74AHC04 能保证的输出信号翻转率很缓(规格书标称的最小翻转斜率为 100ns/V),也就是说,这个电路实际是在用一个低速器件驱动一个高速信号。这样的直接结果便是导致其输出 100MHz 信号时幅度不够;2.源端使用了一个 100ohm 的串阻,负载端使用了一个 200ohm 的并行匹配,从阻抗连续的观点来看, 这种取值起不到阻抗匹配的作用。并行匹配用于 LVTTL/LVCMOS 电平, 也不合适, 100+200=300ohm。电阻的输出负载较重,对信号沿有进一步拉缓的影响;3.100ohm 和 200ohm 的电阻构成了分压网络, 造成 FPGA 输入端的高电平只有 74AHC04 输出端的2/3,这样,接收端得到的信号幅度就更小了。

解决方法:选择沿更快的反相器;串行匹配使用 10~50ohm 的阻值,具体由仿真确定;去除并行匹配电阻。

这个案例主要的问题就在于器件的选型。 100MHz 的时钟,已属于典型的高速信号,用不符合信号沿规格的低速器件驱动,必然会造成信号幅度上的违规。

相关标签搜索:由驱动能力引起的信号完整性案例解读 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析