另解PA输入端匹配电路的作用

2017-06-18 by:CAE仿真在线 来源:互联网

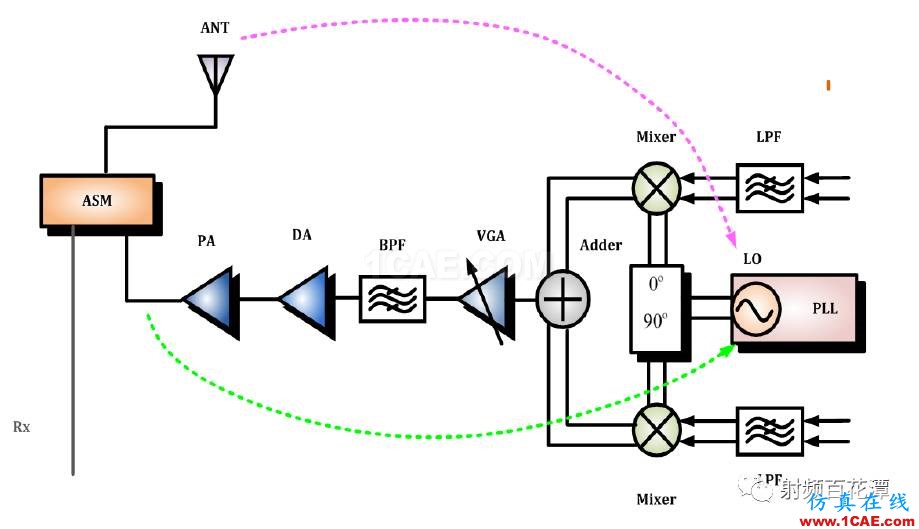

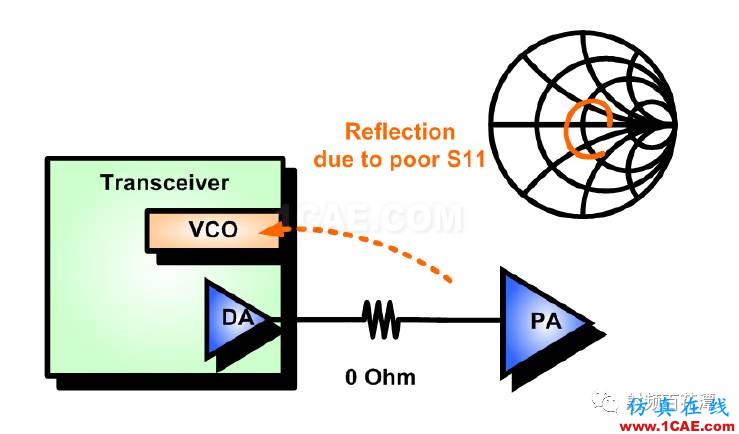

零中频架构收发器,顾名思义,去除掉了中频的零件,由于具备了低成本,低复杂度,以及高整合度,这使得零中频架构的收发器,在手持装置,越来越受欢迎。但连带也有一些缺失,其中一项便是所谓的VCO Pulling,如下图[1-3] :

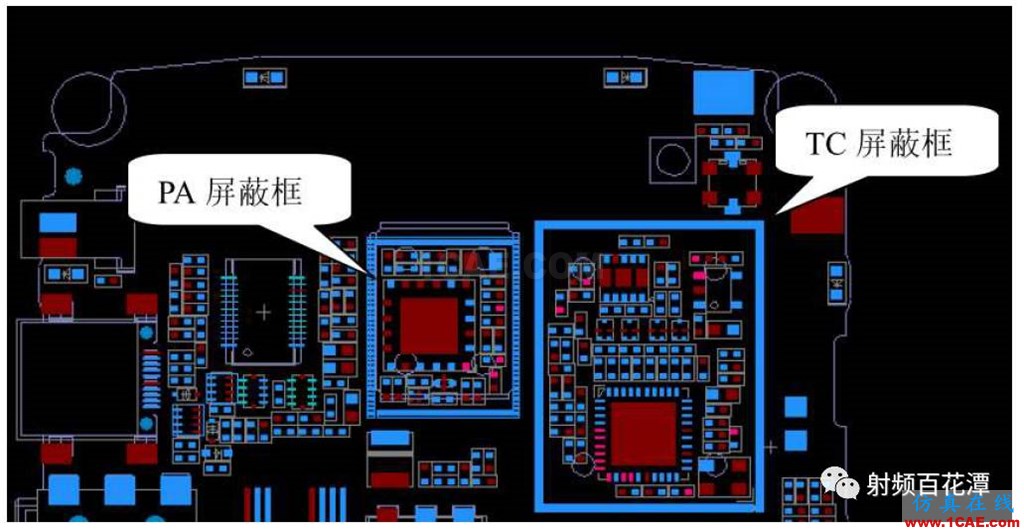

在零中频架构中,因为主频讯号的频率与LO 相同,所以有可能会泄漏并造成干扰,而整个发射路径中,最可能的泄漏来源为PA 输出端与天线端,因为PA 输出端的能量最强,因此会以传导方式干扰,而天线端则是会直接以辐射方式干扰,使调变精确度下降,导致相位误差,频率误差,以及EVM 都会有所劣化。因此不论是高通,或是MTK,都会建议收发器与PA要分别放在两个独立的屏蔽框里,也是为了避免VCO Pulling[1]。

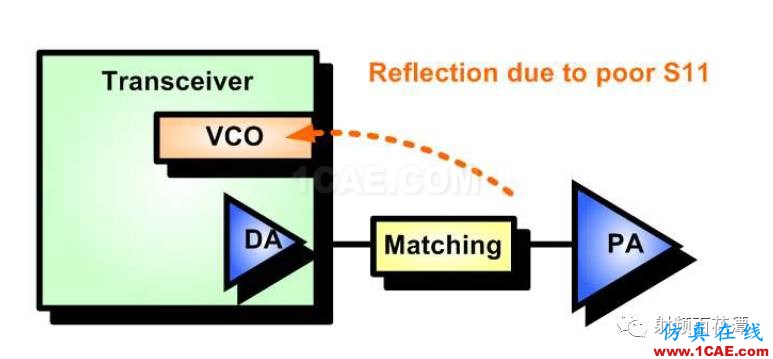

除此之外,PA 输入端的匹配若没调校好,会因反射而干扰VCO,导致调变精确度下降,如下图 :

而PA 输入端的匹配电路,其摆放位置需依平台而定,例如若为MTK 的MT6252,则需靠近收发器,但若为高通的WTR1605L,则需靠近PA。

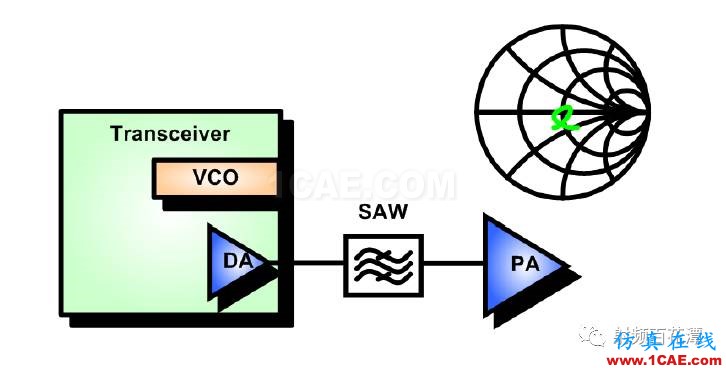

有时会遇到的问题是,将PA 输入端的SAW Filter 拔掉,其相位误差与EVM 会变差,此时可能有人会认为是SAW Filter 的关系,但这是个误解,因为相位误差与EVM,都是带内噪声,而SAW Filter 是用来抑制带外噪声,换言之,SAW Filter无法改善相位误差与EVM,相反地,若SAW Filter 的Group Delay 过大,会导致信号有所失真,进而劣化EVM。

因此合理的解释,便是VCO Pulling,当PA 输入端放SAW Filter,此时收发器看出去的S11 很好,不会有讯号反射。

但是当PA 输入端的SAW Filter 拔掉时,其发射讯号由于Layout 走线阻抗关系,导致收发器看出去的S11 不好,讯号反射打到VCO,使得调变精确度下降,其相位误差与EVM 变差。故此时应针对PA 输入端的Matching 再作微调,以减少反射[3]。

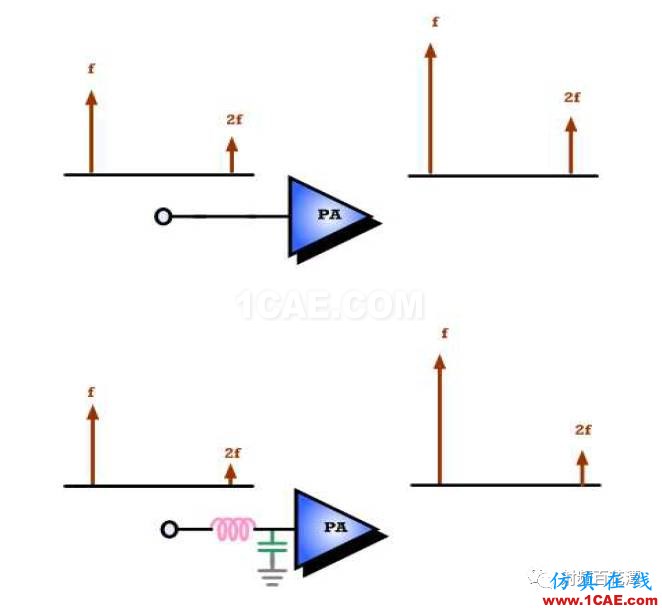

另外,由[4-6]可知,当RF 讯号的谐波过大时,可在PA 输入端,设计LC 低通滤波器,先抑制PA 输入端的谐波,避免因PA 的非线性效应,而使其更加恶化。

特别注意的是,不可将LC 低通滤波器,设计在PA 输出端,因为会动到Load-pull。

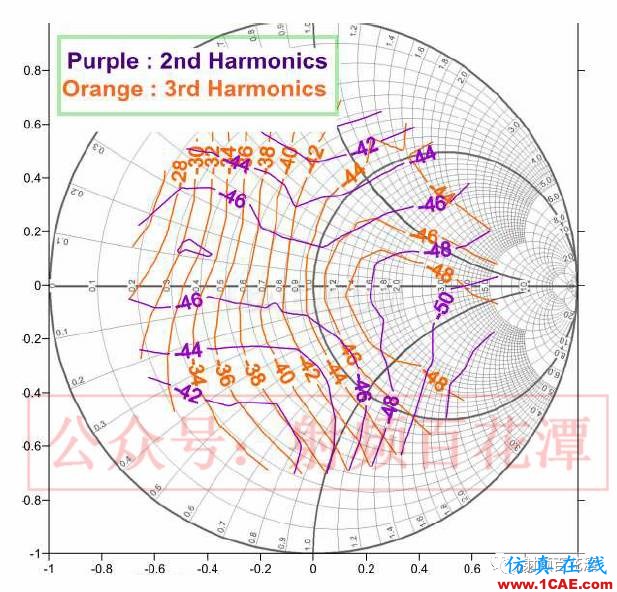

由上图可知,不同的Load-pull,会有不同谐波值,第二象限是高谐波区,若该LC 低通滤波器,使Load-pull 跑到第二象限,进而导致谐波值变大,那么该滤波器抑制谐波的能力,便大打折扣。

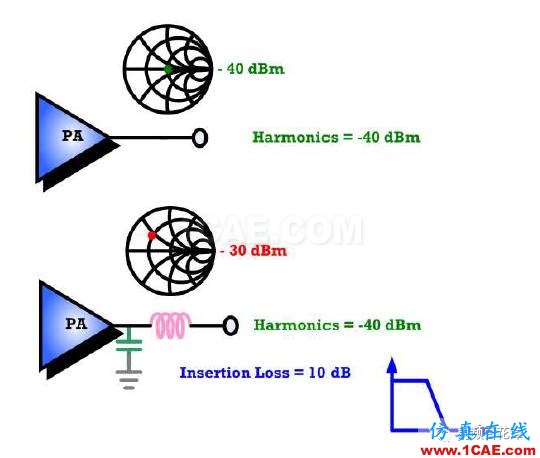

如上图,假设该滤波器,其谐波的Insertion Loss 为10 dB,但因更动了Load-pull,使其谐波增加了10 dB,那么最终谐波会因其抵消结果,而并未所有抑制,故若将LC 低通滤波器,设计在PA 输出端,那么该滤波器抑制谐波的能力,便大打折扣,即便最终谐波仍获得改善,也会因Load-pull 更动,而导致其他发射端的性能都劣化[4-6]。

而由[1-2]可知,PA 的输入端,其实也是DA(Driver Amplifier)的Load-pull :

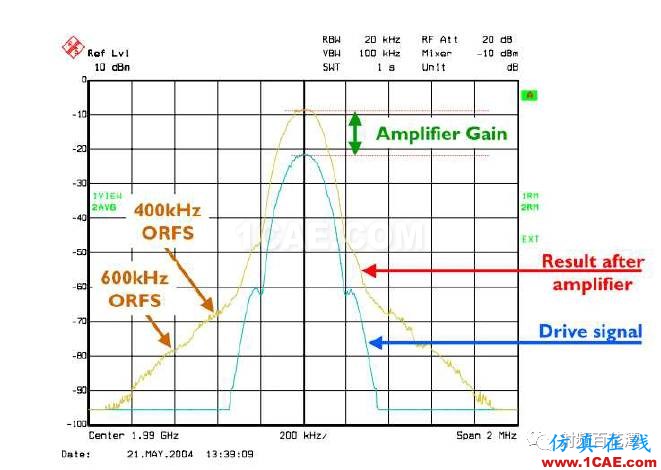

因此这部分的匹配若没调校好,会使DA 的线性度不够,导致在PA 输入端,开关频谱已偏高的情况发生,再加上PA 是主要的非线性贡献者,如此便会导致PA输出端的开关频谱更差。

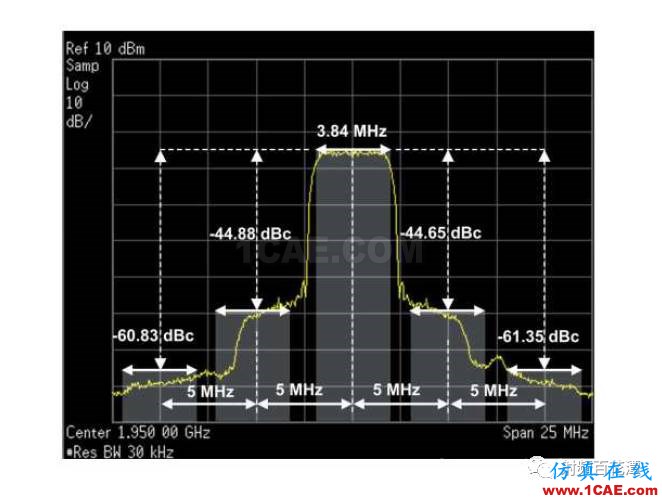

当然WCDMA 的ACLR,也是一样道理,因此PA 输入端的ACLR 不能太差,否则PA 输出端的ACLR,肯定只会更差,而一线品牌大厂,其正负5MHz 的ACLR,都要求至少-40 dBc,

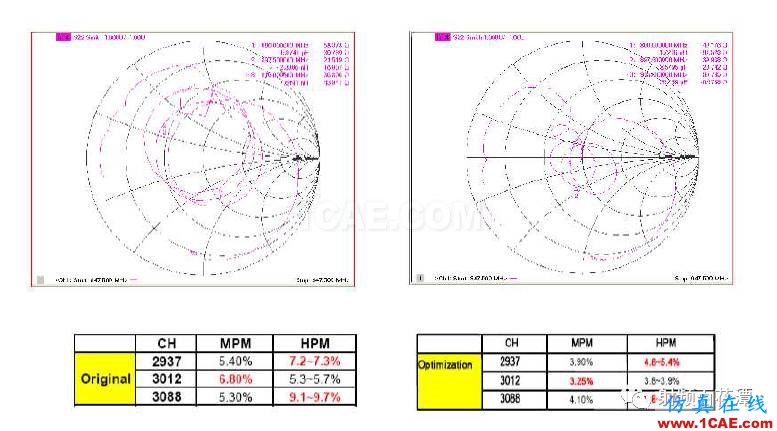

所以PA 输入端,其正负5MHz 的ACLR 至少要-50 dBc。另外EVM 也是一样道理,由下图可知,当PA 输入端的Matching 调校为较收敛的状况时,其EVM 也跟着改善[2]。

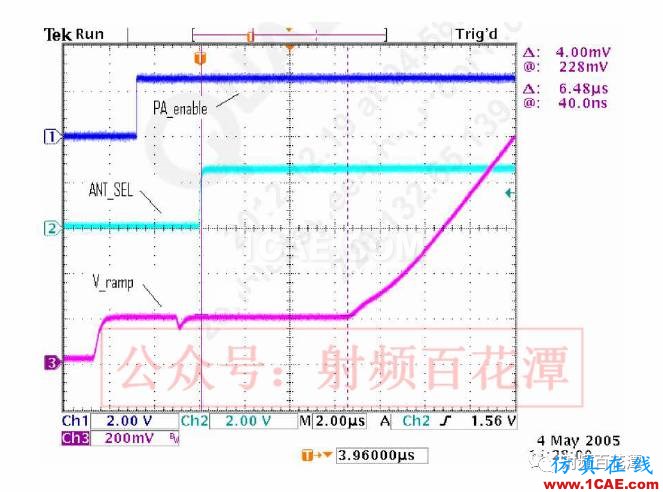

由于PA 的输入功率范围一向很广,以RFMD 的RF3225 为例,其输入功率范围为0 dBm ~ 6 dBm,这表示收发器的输出功率,即便扣掉Mismatch Loss 与Insertion Loss,仍符合PA 的输入功率范围,因此一般而言,较少调校此处的匹配,通常都是要debug 时,才会调校此处。而由以上可以看出,若PA 输入端走线阻抗控制做得够好,有收敛在50欧姆附近,理论上拿掉 是不至于出太大问题。当然,PA 输入端Matching 拿掉,就无法兜低通滤波器,来解传导杂散,不过若是高通平台。还可以靠调NV 的方式来解。下图是PA_Enable、ANT_SEL、V_ramp 三条曲线[1]。

这三条曲线,对于谐波以及开关频谱,都会有影响,建议PA_Enable 比V_ramp早开启,而且最好能早一段时间。而Ant_sel 可以比PA_en 早开启,也可以比PA_en晚开启,看怎样的NV 值 其谐波以及开关频谱会最低。

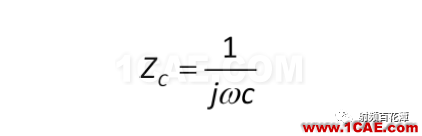

前面提到,若PA 输入端走线阻抗控制做得够好,有收敛在50欧姆附近,理论上其PA 输入端的Matching 可拿掉。而若PA 没有内建DC Block,则PA 输入端需摆放串联电容。然而,由[7-8]可知,串联电容会使阻抗有所偏移,破坏原本已经控制好的阻抗。那这该如何处理呢 ?

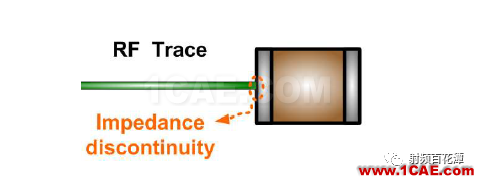

上式是容抗的公式,由上式可知,当电容值极大时,其阻抗会近乎于零。而作阻抗匹配前,要先将落地组件拔除,且串联零欧姆电阻,来得知走线的原始阻抗[8],因此可知串联零欧姆电阻,并不会改变原始阻抗。而前述已知,电容值极大时,其阻抗会近乎于零,相当于零欧姆电阻,故可知若想抵挡直流讯号,但又不想使阻抗有所偏移时,可以摆放大电容,来同时兼具这两种需求。然而这边所谓的大电容,并不需要到uF 等级,因为uF 等级的电容,至少都是0603 的尺寸,若摆放在走线,不仅占空间,同时也会因宽度与走线差异过大,产生很大的阻抗不连续,以至于Mismatch Loss 增加,如下图:

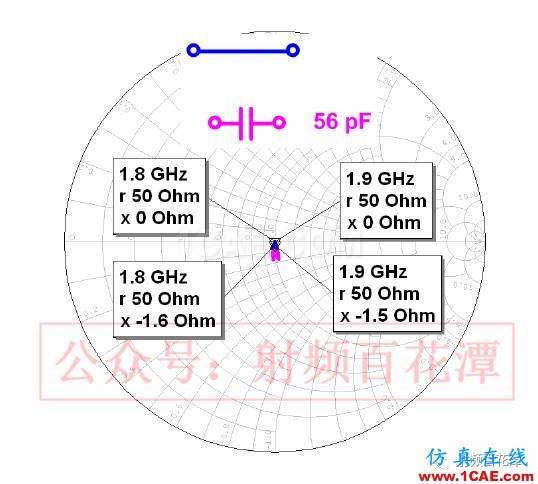

因此pF 等级的电容即可,以DCS 1800/PCS 1900 为例,由下图可知,串联56 pF的电容,其阻抗几乎不变。

由前述我们可总结,PA 输入端匹配电路的作用,主要是用来debug 的 :

1. 频率误差/相位误差, EVM,调制频谱 => 减少反射,避免VCO Pulling。

2. 传导杂散 => 设计低通滤波器,减少谐波。

3. ACLR,开关频谱 => 提升DA 线性度。

若阻抗控制有做好,原则上可以拿掉,以节省空间。但建议初始设计时,还是先摆放,以防万一,确认其发射性能皆无大碍时,下一版PCB 设计再将其拿掉。

Reference

[1] GSM 之调制与开关频谱(ORFS)解析与调校大全, 百度文库

[2] WCDMA 零中频发射机(TX)之调校指南与原理剖析, 百度文库

[3] VCO Pulling 对于零中频发射机之相位误差的危害, 百度文库

[4] 上集_磁珠_电感_电阻_电容 于噪声抑制上之剖析与探讨, 百度文库

[5] 中集_磁珠_电感_电阻_电容 于噪声抑制上之剖析与探讨, 百度文库

[6] 下集_磁珠_电感_电阻_电容 于噪声抑制上之剖析与探讨, 百度文库

[7] 手机射频之阻抗控制, 百度文库

[8] Passive Impedance Matching___实战大全, 百度文库

相关标签搜索:另解PA输入端匹配电路的作用 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析