案例分享之DDR拓扑结构的选择 续

2017-10-15 by:CAE仿真在线 来源:互联网

Fly-by拓扑,驱动到各负载的延时是不同的,是离驱动近的负载信号质量好,还是远离驱动的信号质量好,为什么?我们在学习高速设计的时候,会接触到集总和分布的概念。刚开始并不理解,以为器件之间使用导线连接,保持连通就可以了,然而当信号变化的时间和传输线长在一个数量级的时候,就应该关注传输线效应了,这时候,同一时刻链路上的电压分布会不同,就应该考虑拓扑结构对信号质量的影响。

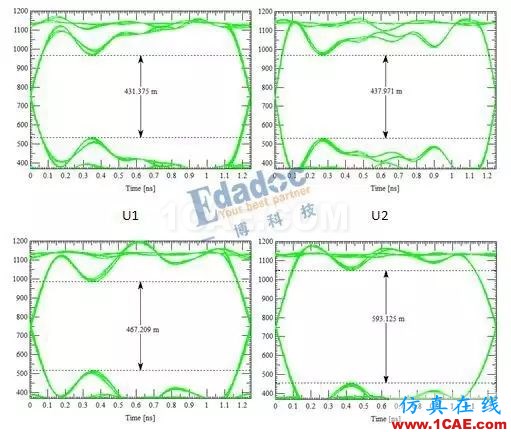

如下图1,对Fly-by四个颗粒的信号质量进行了仿真。其中,信号速率为800Mbps,走线阻抗为50ohm,Stub长度为100mil。

通过对比我们可以发现,尽管U1离驱动器的位置最近,但是对应的眼图幅值最小,原因就是U1的振铃幅度最大,造成U1振铃幅度大的原因就是后续Stub产生的反射能量都传回到了源端。末端因为有上拉端接,反射被抑制了很大一部分,所以信号质量较好。还有一个原因是链路中的stub会产生电容效应,使传到最后的信号上升沿略微变缓,这也使得振铃幅度变小。为了提高信号质量,可以进行容性负载补偿,相关介绍可以查看高速先生前期的文章。文章链接如下:

http://www.edadoc.com/cn/TechnicalArticle/Show.aspx?id=892注:答案提到了近端受到多重反射的影响,以及Stub与负载的容性效应的都是满分。对于离驱动远的DDR颗粒信号质量最好。因为地址与控制命令信号在走Fly-by时,都需要扇出过孔到DDR颗粒,那么必然会存在Stub以及分支,则会导致阻抗不连续(后端分支阻抗变小,反射系数为负)的问题而发生反射,近端的DDR颗粒总是受到后端其它DDR反射回来的信号电压,导致信号质量变差。所以设计时尽量主线路阻抗控制40欧姆,DDR端互连线控制60欧姆,平衡阻抗。另外就是存在ECC校验时,也是建议放置在第一片的位置。 远端会更好,楼上各位大神都提到反射和端接点问题我完全赞同就不再班门弄斧了,从分布电容来讲,距离驱动端越远(不考虑电气长对驱动的影响),线条寄生电容C0会使信号上升、下降沿变缓,可以有效抑制信号的过冲问题,但是也会带来延迟、信号失真等一系列问题,如果系统分辨率可以接受就OK,所以远端信号会更好 Fly-by拓扑要求stub走线很短,当stub走线相对于信号边沿变化率很短时,stub支线和负载就可以看作电容。分布式的容性负载的存在使得靠近驱动端的负载影响最大,远离驱动端的最末端的负载影响最小,信号质量较好。 靠近驱动端时,由于受到后端的多个反射信号的影响,信号质量就变得更差。 通过让负载stub尽可能短,并且负载走线阻抗比主线阻抗高,可以达到整条走线阻抗平衡的目的。 距离驱动远的信号质量更好。 因为Fly-by结构中,stub会引起阻抗变低,且每个分叉都会存在阻抗不连续,信号在stub间反射,叠加后对靠近驱动端的负载上影响最大。 由于末端的端接电阻能较好地消除末端反射问题,而对于分支上的各个反射并不能完全消除。所以,离驱动端远的负载信号相对更好。 离驱动远的颗粒信号质量好。信号从驱动器传输到多个DDR,由于受Stub和阻抗不匹配的影响,存在反射现象,近端DDR总是受到其它DDR反射来的信号,导致信号质量变差。实际画线时主线路阻抗补偿,且尽量减小Stub长度。 远离驱动的颗粒信号质量更好,远离驱动的颗粒靠端接越近,受到反射的影响越小,同时也没其他颗粒引起的反射叠加,信号质量应该更好一些 我们现在遇到的是国产CPU小批量量产出现内存低温不稳定,30片有一半需要单独调试时序参数远端信号质量好,因为一般端接放在远端,线路上的容性负载带来的反射能量,在远端得到最好的吸收,而在线路上越远离端接电阻,被叠加的能量越多。 远离驱动端的颗粒,信号质量更好, 因为Fly by拓扑的每一个stub引入容性负载,会导致走线阻抗变化,影响信号质量,而这种变化对靠近驱动端的颗粒影响更大! 对于地址和控制信号组来说:在控制器输出能力强的条件下(输出电阻低),最后一个ddr3接收到的信号质量最好,反射影响小,容易优化。越靠近主控器,反射越多,信号越复杂,越不容易优化。在控制器输出能力弱,且接了太多颗粒时,末端的信号因获得的能量不足,信号边缘会过缓,点平过低,(可以调节末端vtt阻值优化一下) 离远的质量相对好一些,因为: 1,近端会存在后边节点多处的反射叠加,信号质量更差。 2,反射到原端的能量,在匹配不佳时,返回到近端的能量衰减最小,该反射能量与原信号叠加后信号质量更差。 远离驱动的信号质量好。因为远离驱动端意味着靠近端接,越靠近端接点,信号质量越好。这是因为Flyby结构中信号会由于stub的存在使信号频谱上存在塌陷,此外stub还会使主路径的阻抗发生变化,进而产生发射。由于以上的原因会使得最靠近驱动端的信号质量越差。在实际工程中,除了要尽量减小stub的长度之外,还需要对主路径的阻抗做一些补偿。 我是个初学者 刚学到DDR这块 ,我觉得应该是离芯片远 影响小 因为在信号传输过程中对于阻抗 串扰等 信号会慢慢变的稳定一些吧 不像刚开始那么有大的变化幅度 (1)最后一个DDR3芯片反射叠加最少,信号质量最好,但是得到的能量也最少;(2)前端的DDR3芯片反射叠加多,信号质量差,但得到的能量大。所以,在驱动能力足够的情况下,远端信号最好,若驱动能力不足,则远端信号也会差 DDR的FLY-BY拓扑结构中,远离驱动的信号质量好。越近的受到的stub反射影响越多,每个stub都向前反射。分支越短越好,靠近分支的信号会被多次反射,反射叠加,信号会比较差。信号的反射都是从遇到负载开始,分支越短,反射相对小些。除了反射,还有端接VREF,ODT,CLK,串联电阻的位置,阻抗等多种因素都也都会影响到信号的质量的好坏。 1.从反射的角度来看,末端的ggr3颗粒信号最好,近端的ddr3颗粒会因为多重反射叠加,使得信号质量很差(当然也不能无限远,应该在有效距离内) 2.主控到每一个ddr3颗粒的线长都不应该恰好等于通信频率的谐振长度 远离驱动的DDR芯片信号质量好,因为远端更靠近Rtt,反射的影响最小。靠近驱动端时,由于受到后端的多个反射信号影响,信号质量就变得更差。 Fly-by结构远离控制器的信号质量好,离控制器越近的那片信号质量最差。因为后面几片的反射会叠加过来,同时,最近这片感受的容性负载也是最重的。 距离ddr近的颗粒信号差,由于发送端的信号强,反射影响大 个人认为信号近的质量好,一般远端的信号不好都要靠VTT端接补偿,所以我们的VTT端接电阻都是靠近远端摆放。如果远端的质量都很好的情况下,VTT端接是可以拿掉的。 如果匹配电阻在末端,远离的比较好,如果匹配电阻在近段,修改合适的阻值后,应该近端比较好! 离驱动远的颗粒信号质量好,由于Stub的作用,存在反射的作用,受到其他的反射信号,信号质量变得更差,因此应该尽量减少Stub的长度 离驱动近的负载信号质量好点,越远越差,因为根据阻抗的公式,远端的会有分布电感和电容效应,阻抗会减少,随着传输线增长会有变化,导致阻抗不连续,信号质量不好在驱动能力足够,终端负载在一定长度范围内的情况下,远离驱动端的信号质量要好一些,因为离驱动端越近的负载接收到该负载之后的反射越多,结果是多个负载反射的叠加到信号上面,干扰越大。 远离驱动的信号质量好。因为 远离驱动的信号受到的反射要少些,其过冲小些。 理想情况下,驱动源内阻R0=传输线特征阻抗Z0=负载内阻RL,传输线的阻抗是连续的,不会发生任何反射,能量一半消耗在内阻,一半能量消耗在负载。信号传输路径越短,不可控阻抗情况越少,质量信号也就越好。 远的好,最末端一个效果最好;没有后面一级带来的反射反射

开放分享:优质有限元技术文章,助你自学成才

相关标签搜索:案例分享之DDR拓扑结构的选择 续 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析

编辑