DDRx的关键技术介绍(上)【转发】

2017-10-13 by:CAE仿真在线 来源:互联网

在上一篇的问题里面问到了DDRX相对于前一代来说的关键技术突破在哪里,虽然没有人回答得完全正确,但这个也是很正常的,因为通过几句话要想说清楚也确实是不容易的,所以还是通过文章来把这些关键技术再给大家介绍一下。

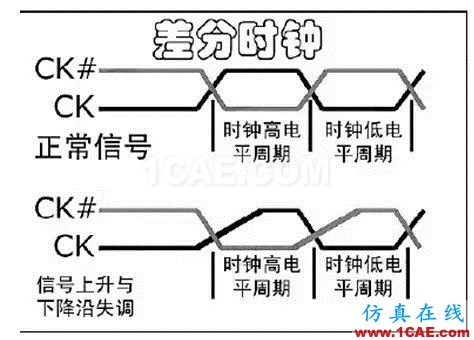

差分时钟是DDR的一个重要且必要的设计,但大家对CK#(CKN)的作用认识很少,很多人理解为第二个触发时钟,其实它的真实作用是起到触发时钟校准的作用。

由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的CK#(CKN)就起到纠正的作用(CK上升快下降慢,CK#则是上升慢下降快),如下图一所示。

图一 差分时钟示意图

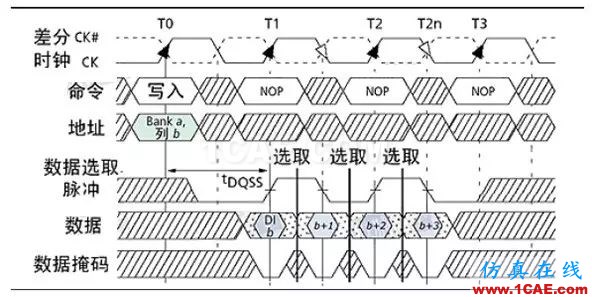

就像时钟信号一样,DQS也是DDR中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗8bit DRAM芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由主控芯片发来的DQS信号,读取时,则由DRAM芯片生成DQS向主控发送。完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为tAC。实际上,DQS生成时,芯片内部的预取已经完毕了,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。由于是并行传输,DDR内存对tAC也有一定的要求,对于DDR266,tAC的允许范围是±0.75ns,对于DDR333,则是±0.7ns,其中CL里包含了一段DQS的导入期。

DQS 在读取时与数据同步传输,那么接收时也是以DQS的上下沿为准吗?不,如果以DQS的上下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是为什么要有一个tAC规定的原因。而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。这样在写入时,DRAM芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的,如下图二所示。

图二 数据时序

不是DDR所特有的,但对于DDR来说也是比较重要的技术,所以一并介绍下。

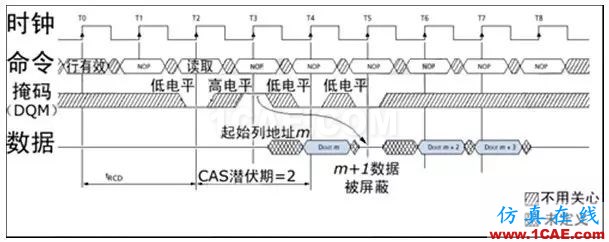

为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技术。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

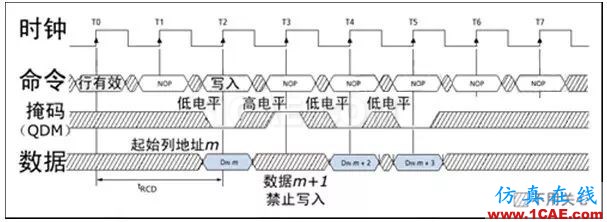

DQM由主控芯片控制,为了精确屏蔽一个P-Bank位宽中的每个字节,每个64bit位宽的数据中有8个DQM信号线,每个信号针对一个字节。这样,对于4bit位宽芯片,两个芯片共用一个DQM 信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于16bit位宽芯片,则需要两个DQM引脚。SDRAM 官方规定,在读取时DQM发出两个时钟周期后生效,而在写入时,DQM与写入命令一样是立即生效,如下图三和四分别显示读取和写入时突发周期的第二笔数据被取消。

图三 读取时数据掩码操作

图四 写入时数据掩码操作

所以DQM信号的作用就是对于突发写入,如果其中有不想存入的数据,就可以运用DQM信号进行屏蔽。DQM信号和数据信号同时发出,接收方在DQS的上升与下降沿来判断DQM的状态,如果DQM为高电平,那么之前从DQS中部选取的数据就被屏蔽了。

有人可能会觉得,DQM是输入信号,意味着DRAM芯片不能发出DQM信号给主控芯片作为屏蔽读取数据的参考。其实,该读哪个数据也是由主控芯片决定的,所以DRAM芯片也无需参与主控芯片的工作,哪个数据是有用的就留给主控芯片自己去选择。

前面介绍了DQS的功能,那么我们在测试时根据DQS和DQ的波形是如何区分数据的读写操作的?

原作者及出处——一博科技“高速先生” 作者: 周伟

相关标签搜索:DDRx的关键技术介绍(上)【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析