等长只是时序控制的开始【转发】

2017-10-13 by:CAE仿真在线 来源:互联网

DDR线长匹配与时序(下)问答码间干扰和串扰是怎么影响时序的?在讲到影响源同步时序的因素中,我们更多强调的是时钟与数据的等长,因为等长后基本就等时了,等时后驱动端时钟与数据之间的相位关系就能被准确无误的传输到接收端。然而,在保证时钟与数据同时到达接收端的前提下,信号质量还会受到其他因素的影响。有时候,尽管时钟与数据同时到达了接收端,然而他们已经“物是人非”,接收端已经无法看清他们本来的面目。所以,等时只是保证信号时序的第一步,关键的还是要控制好信号的质量,否则,接收端同时传来被“玩坏”的时钟与数据,也是功败垂成。码间干扰和串扰会影响时序吗?答案是肯定的。然而到底是怎么影响的?这个就有点不好说了,因为这个问题比较抽象,要想回答清楚就得详细说说他到底影响了时序的哪个参数。是建立时间裕量,还是保持时间裕量?

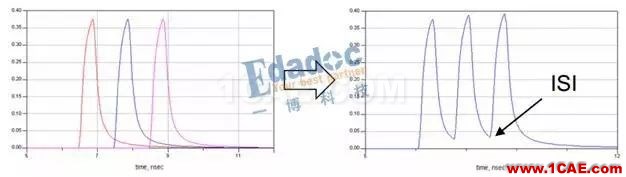

首先必须弄清楚什么是码间干扰(ISI)。大家应该都了解串扰,串扰指的是由于信号线之间的互容和互感作用,本来传输的信号电压和电流会被相邻信号线拉高或者降低,使得信号失真的情况。码间干扰也一样,由于互连通道对不同频率衰减不同,导致信号边沿变缓,因此单个脉冲的宽度会变宽,形成“拖尾”,延伸到下一个bit位,如下图1所示,这种延伸会改变下一位脉冲的幅度,从而使波形失真。

图1 码间干扰

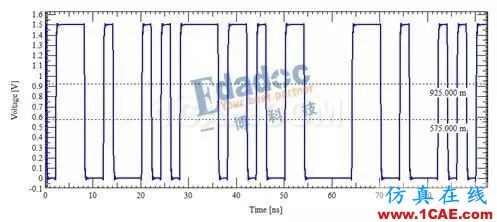

仿真实例如图2所示,图2是驱动端码型

图2 驱动端波形

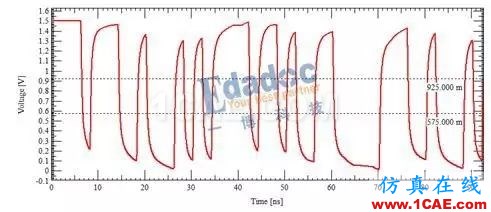

经过30inch的传输线后,波形如图3所示

图3 接收端波形

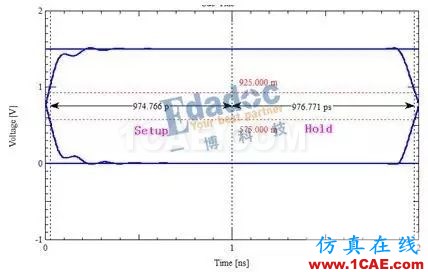

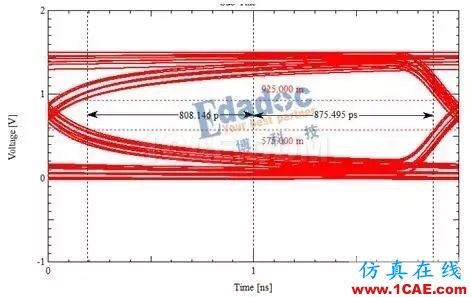

下面我们通过眼图来看看时序参数,驱动端信号时序参数如下图4所示:

图4 驱动端眼图

图5 接收端眼图

看来,等长只是时序控制的开始,为提高信号的时序裕量,我们要做的还有很多呢。

下面来看下各位网友的答题情况:注:回答出了码间干扰的产生机制,以及对具体时序参数的影响都是满分。(以下内容选自网友答题)码间干扰就是在同一个时隙中,不同码道之间存在时间不同步,就是有偏移。信道的非理想(这里指不是无限宽的频带)和多径效应都会产生时域上的码间相互串叠。由于电磁耦合而在相邻的传输线上产生不期望的电压或电流噪声干扰:Jenny评分:2分码间干扰和串扰会带来线路之间的时序不平稳,对于时钟会带来抖动和偏移等现象,还会使得信号眼图变差,影响时序建立和保持时间:zhl评分:2分当码间串扰严重时,会造成错误判决,即本来的0被判断为1,1被判断为0,从耳导致时序错误:涌评分:2分码间串扰是由于系统传输总特性不理想,导致前后码元的波形畸变、展宽,并使前面波形出现很长的拖尾,蔓延到当前码元的抽样时刻上,从而对当前码元的判决造成干扰。码间串扰严重时,时序会造成错误判决。以DDR举例,时序是信号来判决的,码间串扰会使时序得到相反的电平,从而影响芯片误操作。通过眼图可以知道码间串扰程度,眼图的眼睛张开得越大,且眼图端正,表示码间串扰越小,反之表示码间串扰越大。:Lee评分:3分串扰,能量感性与容性的耦合。改变受到串扰的传输线的特性阻抗与传输速度,也改变了信噪比,这些都会影响时序判别。码间干扰,造成信号之间互耦,造成时序错乱。: Jamie评分:2分如果之前的长时间内位序模式为高,接着降低一位后再升高,则此位低电平很难降低到最低电压值,此时,数据的建立时间和保持时间就有问题,这是码间干扰的影响。串绕主要是走线之间容性耦合和感性耦合的影响,同样会使信号边沿受到影响,使建立时间和保持时间就有问题。: 王发展评分:2分码间干扰:指单个信号线上的相邻的“1”和“0”电平相互干扰,前一位数据使得后一位数据的UI时间减少,上升下降的边沿缓慢。由以下公式[Tva(由建立时间、建立时间裕量和vref到阀值的时间组成) + Tvb(保持时间、保持时间裕量和vref到阀值的时间组成)=UI ]可知:建立时间裕量和保持时间裕量会减少,导致系统误码率高; 串扰干扰:由于相邻的信号线上有电平转换,(1变0或者0变1),变换电平会产生变化的磁场,变化的磁场会被信号线感应到并产生电平的叠加,这样会干扰信号的上升、下降时间和电平,导致建立时间裕量和保持时间裕量会减少,而且噪声容限也会减少,导致系统误码率高。:海鸥评分:3分1.码间干扰是指信号传播时,前一位数据与后一位数据不同时,前一位会导致后一位的上升或下降时间变缓,出现不规则无法避免的抖动,降低建立保持时间裕量。2.串扰则是由于附近的其他信号发生翻转,且上升下降沿很陡,这时信号线会有感应,产生有能量的叠加,造成信号上升下降时间更陡或更缓,降低建立保持时间的裕量。3.在高速信号通信中,严重的情况下,两者都会导致系统通信误码率升高。:小叶紫檀评分:3分建立时间和保持时间的和小于UI,因为还有建立时间裕量、保持时间裕量等。速率越高,就是UI越小,会导致建立时间裕量、保持时间裕量也越小,以及串扰、抖动等干扰因素,容易产生信号的误判,从而更难进行时序控制。:杆评分:3分码间干扰是由于阻抗不匹配等原因,使接收端当前码元信号受到之前码元信号的干扰(如反射信号)。串扰是不同位信号之间的耦合。对于DDR来说,DQ信号是同时跳变的,所以DQ信号的串扰都在跳变沿,会影响slew rate,从而产生jitter,而DQS跳变位于DQ信号的中心,产生的串扰影响更大,所以通常要加大DQS与DQ的间距。码间干扰同样会影响slew rate,并产生抖动,所以需要控制阻抗,减少反射。: 绝对零度评分:3分码间干扰,当前一个码还没有稳定时,后一个码已经在路上了,使得前一个码的反射、串扰对后一个码产生影响,造成码型的变化,从而使得信号畸变或偏移,最终反应到时序上。而串扰,主要是微带线对奇模和偶模信号的介电常数不同引起的。当骚扰线和受害线同向时,大部分电磁场进入介质,受害线信号速率比正常情况降低,而反向时,则反之,最终速率的变化也对应到时序上。:大海象评分:3分1,在高速并行总线链路中,码间干扰是由于高低电平的不平衡,导致持续的1或0电平出现后,信号电平反转时,会使信号不能拉低或拉高,同时,信号边缘变缓,数据的边沿无法对齐,影响建立和保持时间,从而导致出现误码。 窜扰,多位数据信号并行走线且间距较小时,数据同时并行翻转,由于耦合关系,会对相邻数据位有干扰,比如边缘的毛刺、高低电平的振铃等,会吃掉一定的建立保持时间裕量,影响到时序。 3,码间干扰和窜扰对于高速串行总线的影响比较大,导致接收端的时钟信号抖动偏大甚至无法恢复,从而会减小建立保持时间。:hk评分:3分建立时间+保持时间小于ui。速率越高,余量越小,留给调整的范围越小,所以时序越难控制。: 涌评分:2分码间干扰是因为信号传输路径长,当信号速率较高时,由于系统传输总特性不理想,导致前后码元的波形畸变,并使前面波形出现很长的拖尾,蔓延到当前码元的抽样时刻上,从而对当前码元的判决造成干扰。码间串扰严重时,会造成错误判决。串扰则是因为相互传输线间的互感互容,当噪声脉冲叠加到被干扰网络,就会引起被干扰网络信号传输延时减少或增加,由于干扰源网络的不确定性,这种延时是无法控制的,因而对这种串扰引起的延时必须加以控制。: 刘栋评分:3分码间干扰是由于有限信道带宽决定的,当信号在有限带宽信道中传输时,在时域会有拖尾,如果拖尾在其它符号抽样处不为0,则造成码间干扰;码间干扰造成信号元相互干扰,会使信号的抖动增加,从而影响时序。串绕分远端和近段串绕,当信号线相互靠近时,信号线上的信号电平发生快速反转时,会在相邻信号线感应出电平,若果电平正好相反时,会时信号的上升沿或者下降沿时间变长,从而导致其采样电平点发生偏移,影响建立时间和保持时间:Jasen评分:3分码间干扰:是前、后码元的波形畸变、时延、展宽等,导致建立时间裕量和保持时间裕量减少,信号畸变或偏移,使得误码率高,影响时序。串扰:是相邻信号线之间的电磁耦合引起的,产生尖峰、额外延时,使得保持时间裕量减少,噪声容限减少,从而影响时序。: 龍鳳呈祥评分:3分码间干扰是由于传输特性不理想,导致前后码元的波形畸变、展宽、时延等,并使前面波形出现很长的拖尾,从而导致判定本码元脉冲波形的值时与其它脉冲波形的拖尾相叠加。本质上,导致建立时间裕量和保持时间裕量减少,使得系统误码率提高,影响了时序。 串扰是由于相邻走线之间的耦合引起的,会导致产生尖峰噪声、额外延时,尤其是相邻走线信号同时翻转时。信号边沿受到影响后,以及抖动影响使得时间裕量噪声容限减小,从而影响了时序。:杆评分:3分(1)码间干扰,由于通信速度过高,走线长,插入损耗S21太低,信号在1和0相互变换时,能量释放太慢,前一位的信号能量影响后一位的信号能量,使得整个UI的抖动增加,建立保持时间裕量变小,通信容易出现误码率高的问题。(2)串扰,附近的信号发生跳变时,产生方向不同的变化的磁场,会在信号线上叠加或正或负的能量,使得整个UI的抖动增加,电平有纹波,减少建立保持时间裕量和噪声容限,误码率高。:Ben评分:3分码间干扰:一个信号线上相邻码元发生变化时,会导致后一位的上升或者下降沿变缓,降低建立时间和保持时间的裕量;串扰:与之相邻信号线数据发生高速变化时,由于电磁感应耦合到本身,对建立时间和保持时间产生影响。:Ku评分:3分码间干扰指的是相邻码元之间的电平干扰,码间干扰除了会引起码元的错误判决、增加误码率之外,还会抬升被干扰码元的边缘,是边缘退化,从而影响时序。 串扰是入侵线的能量通过容性干扰和感性干扰耦合到受害线上,如果串扰表现为正脉冲,则会抬升受害线的边缘,而与此同时入侵线由于能量损失了一部分,就会造成边缘的退化,由此影响时序。:黄跃辉评分:3分1.高速信号传输通道有一定的带宽限制,信号通过该通道边沿变缓,拖尾影响下一位信号,使信号偏离原先的位置,抖动增加。2.当串扰噪声叠加到信号边沿上,会引起信号边沿畸变,可能使信号提前或延迟。进而导致边沿的抖动,结果是时序裕量减小。:山水江南评分:3分码间干扰:由于通道存在冲击响应,并且高电平变为低电平时高频分量存在严重拖尾效应,尤其是高速链路场景多个连1后突然变为0时特别明显,会使得本该0电平的电位降不到0,数据的边沿无法对齐,影响建立和保持时间,从而导致出现误码。 串绕:由于DDR是多位数据同时并行翻转,由于感性和容性的存在,会对相邻数据位有干扰,导致正常数据的电平裕量降低,边沿变缓,从而影响到建立和保持时间的窗口,影响到时序。:杨勇评分:3分

原作者及出处——一博科技“高速先生”

开放分享:优质有限元技术文章,助你自学成才

相关标签搜索:等长只是时序控制的开始【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析

编辑