如何用TDR来测试PCB板的线路阻抗【转发】

2018-04-10 by:CAE仿真在线 来源:互联网

隔壁小王已经讲了TDR的原理以及如何确定TDR的分辨率。那么,我们要正确测量PCB板上的线路阻抗,还有哪些需要注意的地方呢?

阻抗测试的行业标准

之前贴过好多张阻抗测试的图片,重新再贴一张给大家看看。阻抗并不是想象中稳定的直线,而是波澜起伏。在前端和后端会受到探头或者开路的影响,中间由于生产制程的关系,也会有波动。

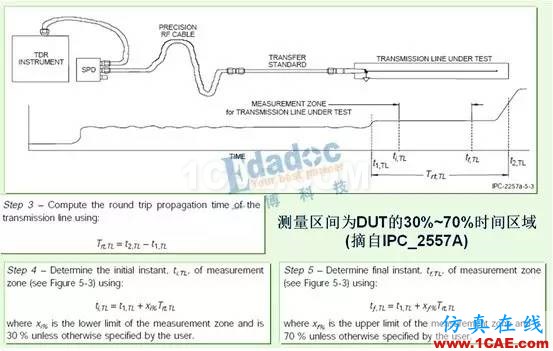

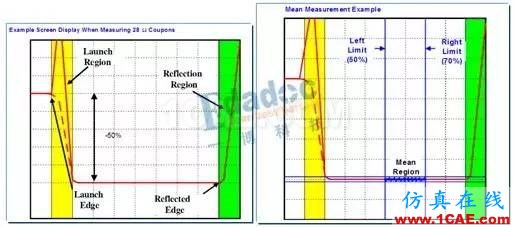

那么,我们怎么判断测试结果呢?怎么确定生产出来的PCB阻抗是否满足要求呢?首先来看看IPC规范,IPC2557A建议的测量区间是DUT的30%~70%区间。

再来看看Intel以及现在主流板厂的测试习惯,为了避开Launch区域以及反射区域的影响,测试区间建议是DUT的50%到70%区域。

用TDR来测试线路阻抗,我们首先要了解测试区间的要求,才能准确理解测量得到的结果。

探头对阻抗测试结果的影响

通常来说,TDR测试的时候,会用以下几种探头:

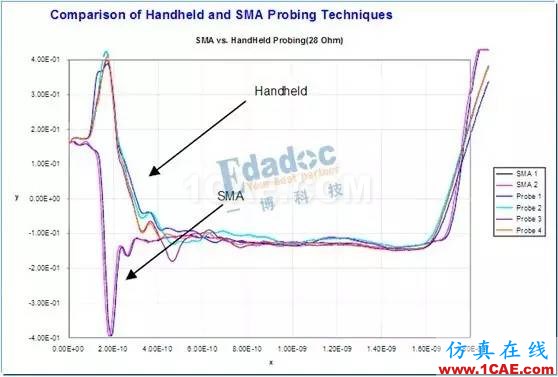

其中,板厂通常会用手持探棒点测,Probe的影响呈现感性。SI实验室常用SMA来连接测试线缆,SMA在阻抗测试中可能呈现容性。两种探头对测试结果的影响如下图所示:

由于Probe的感性或者容性影响,最终DUT的测试结果会有一点点的偏差。

作为本期阻抗话题的结尾,以及引导一下后面的话题

转自公众号:一博科技高速先生 作者:作者: 吴均

相关标签搜索:如何用TDR来测试PCB板的线路阻抗【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析