高速信号短链路问题

2019-03-15 by:CAE仿真在线 来源:互联网

系统设计上,长链路设计上大家都有足够的重视。

-

Serdes厂家研发的时候,大部分的重点都放在长链路的情况。毕竟Marketing要拿这个数据跟竞争对手去PK的

-

有条件的公司在设计新系统产品的时候,在评估各家芯片方案时,也花了足够多的时间在系统的衰减最大的通道也做了足够评估

既然大家都做了那么多的工作,长链路出问题的可能性相对就少啦。最后往往是短链路出问题。什么原因呢,这里分享一下几点看法:

1.PCB设计

绝大部分情况下,短链路问题不可能在供应商的评估板上复现,因为评估板设计的时候,都是设计给评估芯片IO的性能的,所以链路会很简单很干净,这样可以真实评估芯片的性能。

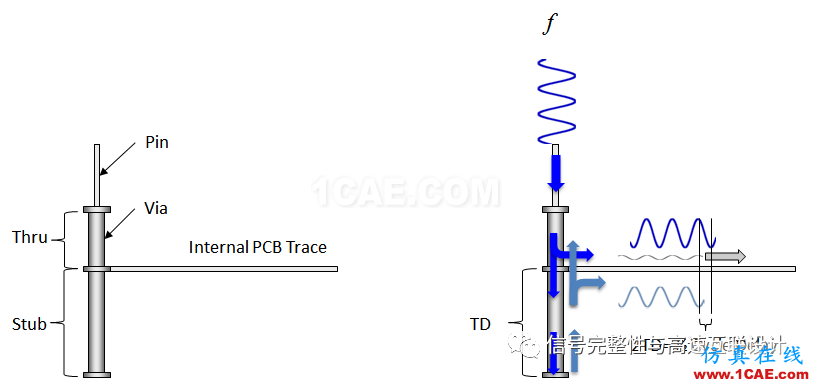

但是一个实际应用上,链路上会至少有两个过孔,可能还有连接件。链路上连接器,过孔,和芯片内部的多次反射信号叠加到原来信号上,使得链路Margin变小。这个问题在短链路的时候更严重,因为反射信号没有被衰减多少。

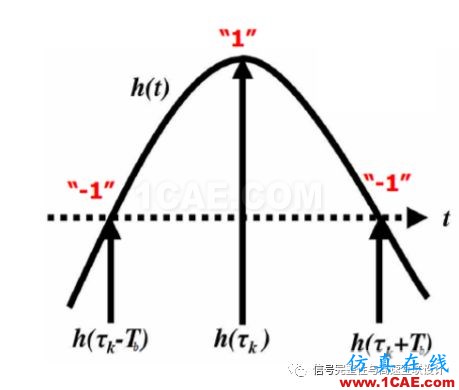

最常见的问题是Stub, Stub留多长会是比较好呢。按照谐振点出现在7次谐波的位置,对于28Gbps NRZ信号,Stub最好控制在12mil以内(出处在文末链接)。当Stub长度是信号波长的1/4时,这个时候从stub端反射回去信号变成了180度反相,叠加到原来信号上。这个时候如果输入是正弦波的话,输出那边就什么信号也没有了。这个信号频率就是这个电路的谐振点。

2.发送端预加重

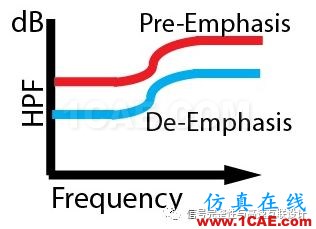

短链路情况下,通常接收机内部的CTLE和DFE就可以很好补偿链路衰减了。这样板内通信的时候,就不需要在对端发送端加任何的预加重设置。在面板应用的时候,有些光模块缺省就有一些预加重,波形在模块厂家的测试平台上眼图最漂亮。但是在实际应用上,这个时候适得其反。

预加重从频域上看就是一个高通滤波器。

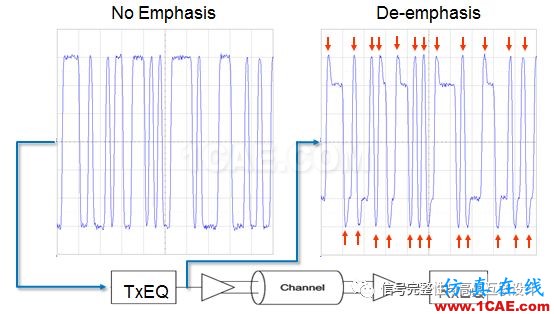

从时域上看如下图。如果通道衰减很小,在RX端输入的波形还是有预加重的波形,有些时候会影响接收机的工作。

3.接收端均衡

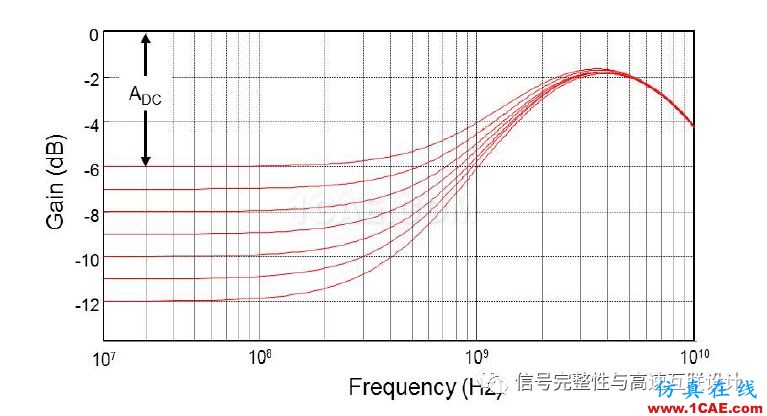

有些芯片供应商的的最小EQ Boost不是0 dB,比如下图来自某标准。芯片内部通常是没办法Bypass CTLE电路的,任何一个Feature都是有成本的。这样在短链路的时候,信号会过均衡。

4.接收端CDR架构

有些CDR的架构,导致短链路情况下不够强壮。具体就不展开了。

低温下,PCB衰减变小,芯片信号沿变快,短链路出问题的可能性就更大了。

相关标签搜索:高速信号短链路问题 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析