Memory系列之--DDR(内存)时序怎么读

2019-03-15 by:CAE仿真在线 来源:互联网

对于大部分工程师而言,Memory在设计中经常会非常困难,这种困难,来源于数目繁多的各种信号线,来源于各种不同的拓扑结构,更来源于JEDEC Spec中让人眼花缭乱的时序图……然而,这终究是需要迈过去的一道坎

从JEDEC的Specification中可以看到Memory相关的Timing十分复杂. 但如果只是分析信号完整性, 大部分复杂的时间参数都可以忽略, 以下就DDR3-1333 2R*8 Unbuffered Memory为例, 对只同信号完整性相关的一些时间参数做一个回顾。

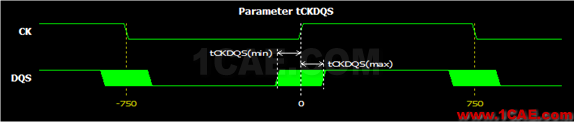

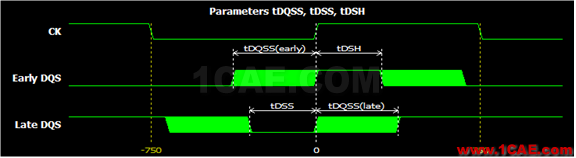

写数据是从Controller写入数据到DRAM. 参考JEDEC 2R*8 的Topology可以知道, 相同Rank内共用同一Clock信号, 一个Rank共64bit数据, 每8bit为一组对应自己的DQS信号, 所以在同一Rank内共有8个DQS同Clock在信号写入时边缘对齐.由于芯片内部差异, 发送端DQS同Clock时间差值为tCKDQS (DDR3-1333 Spec: ±100pS).到达接收端, 即DRAM端时, 由每个DQS及Clock线长的不匹配而引起到达时间的差异记为tDQSS, 其值在±0.25tCK之间 (DDR3-1333 Spec: ± 375pS). 同时如果tDQSS>0, 即DQS晚于Clock到达DRAM, DQS的前一个下降沿和Clock的上升沿的时间间隔tDSS>0.2tCK (DDR3-1333 Spec 300pS). 如果tDQSS≤0, 即DQS早于Clock到达DRAM, 则DQS的下一个下降沿同Clock上升沿之间的时间差tDSH>0.2tCK (DDR3-1333 Spec 300pS).

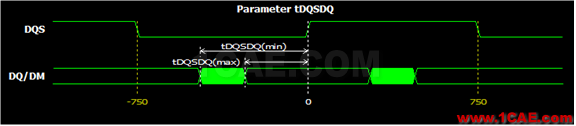

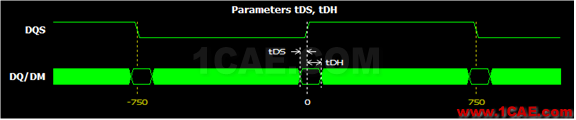

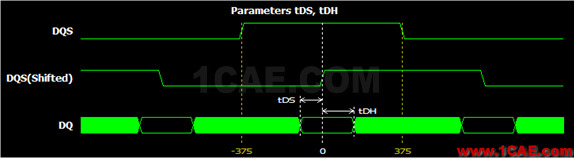

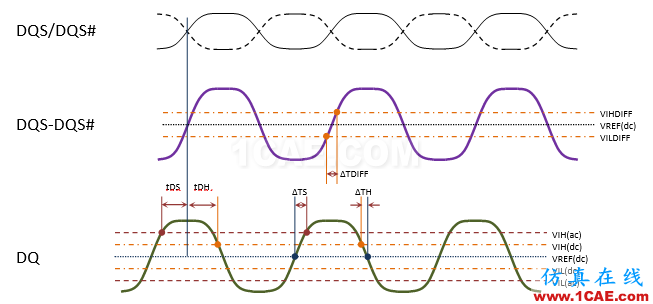

在写入数据时, 每组数据内DQS的上升沿将触发DQ/DM代表的电平写入DRAM中. 同样发送端组内DQ/DM相对于DQS的差异tDQSDQ在-475pS~-275pS之间(DDR3-1333).在到达DRAM时, DQS的边缘应对齐于有效DQ/DM时间范围的中心. DQ/DM的Setup Time为tDS, Hold Time为tDH.

2读取数据

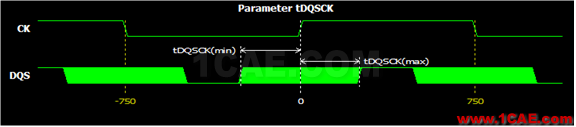

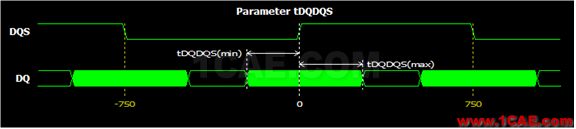

读取数据是将数据从相应的DRAM中读到Controller中. 在DDR信号中DQS/DQ/DM是可以双向传输的信号. 而其他Clock/Address/Command/Control信号都是单向传输信号, 只从Controller发送, DRAM接收. 在数据读取时, Clock的上升沿触发DQS/DQ/DM信号同时从DRAM端发出, DQS上升沿相对于Clock上升沿的Delay为tDQSCK (DDR3-1333 Spec ±255pS以内), DQ跳变沿相对于DQS边缘的delay为tDQDQS (DDR3-1333 Spec: -180pS ~ 125pS).

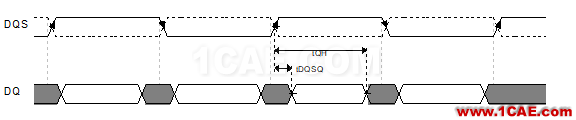

信号从DRAM传输到Controller, DQ同DQS间的时间差记为tDQSQ, DDR3-1333中tDQSQ < 125pS, DQ Hold Time tQH > 0.38tCK (DDR3-1333 Spec: 570pS). Controller内部将DQS延时1/4tCK (90⁰相位提升) 后作为DQ的触发信号, 所以相位提升后的DQS的上升/下降沿对齐于有效DQ信号的中心.

3ADD/CMD/CTL写入时序

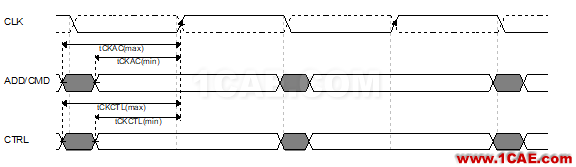

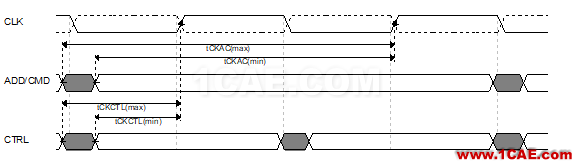

ADD/CMD/CTRL是单向传输信号, 只从Controller发送到DRAM颗粒, 同时不同于数据线的双倍速率传输, 在DDR1/2/3中ADD/CMD/CTRL都是单倍速率传输的. 也就是说每一个Clock的周期内最多传送1位的ADD/CMD/CTRL指令, 比如Clock的频率为667MHz时, ADD/CMD/CTRL的最大频率为333MHz. 在发送端, 即Controller一侧, Clock的上升沿对齐于有效AMD/CMD/CTRL的中心. 但通常ADD/CMD的负载多, 拓扑结构复杂, 当时钟频率越来越高时, 在接收端, 一个时钟周期内不能绝对保证ADD/CMD的建立保持时间满足要求. 此时Controller会将ADD/CMD的数据有效时间扩大到2个时钟周期, 以保证指令的正确传输.在发送端每个时钟周期内ADD/CMD/CTRL值都发生变化的时序称为1T Timing, 每2个时钟周期内ADD/CMD发生变化的时序称为2T Timing, 2T Timing多见于内存时钟频率大于等于800MHz的系统中. 1T Timing中tCKAC/tCKCTRL是ADD/CMD/CTRL有效到第一个Clock上升沿的时间差 (DDR3-1333 Spec: -900~-600pS; AMD tADDRskew = tCKAC(max) – tCKAC(min) = 0~100pS), 2T Timing中tCKAC是ADD/CMD/CTRL有效到第一个Clock上升沿的时间差 (DDR3-1333 Spec: -2400~-2100pS).

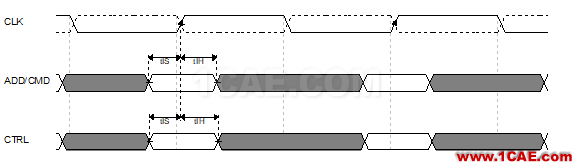

对于每个DRAM颗粒, 输入的Clock信号应与有效的ADD/CMD/CTRL中心对齐. ADD/CMD/CTRL的建立保持时间分别为tIS和tIH.

4建立保持时间的计算方法

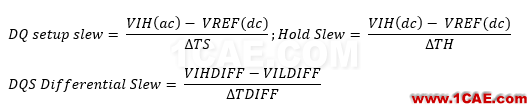

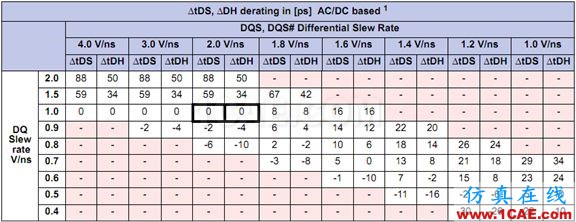

在JEDEC标准中对了DDR3 DRAM颗粒上接收到的DQ/ADD/CMD/CTRL的建立保持时间标准有一个复杂的定义. 下面通过DQ建立保持时间的计算的示例来说明.

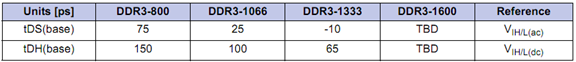

For DDR3-1333, tDS(base) = -10ps; tDH(base) = 65ps

IfDQ Setup slew = 2.0V/ns;

DQ Hold slew = 1.5V/ns;

DQS Differential Slew = 2.0V/ns

ThenΔtDS = 88pS; ΔtDH = 34pS;

SoDQ Setup Spec = tDS(base) + ΔtDS = -10pS + 88pS = 78pS;

Hold Spec = tDH(base) + ΔtDH = 65pS + 34pS = 99pS;

The measurement result: tDS ≥ 78pS, tDH ≥ 99pS.

Note:for more Slew calculation details, please refer to the JEDEC79-3A

5问题

以上以DDR3为例说明了DDR时序相关的内容,那么,DDR4呢?

相关标签搜索:Memory系列之--DDR(内存)时序怎么读 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析