高速串行差分信号的PCB设计与仿真

2017-06-26 by:CAE仿真在线 来源:互联网

随着电子设计技术的不断进步,要求更高速率信号的互连。在传统并行同步数字信号的数位和速率将要达到极限的情况下,开始转向从高速串行信号寻找出路。HyperTansport(by AMD), Infiniband(by Intel),PCI-Express(by Intel)等第三代I/O总线标准(3GI/O)不约而同地将低压差分信号(LVDS)作为下一代高速信号电平标准。本文将从LVDS信号仿真、设计,等多方面探讨合适的LVDS信号的实现。

✿

前 言

随着近几年对速率的要求快速提高,新的总线协议不断的提出更高的速率。传统的总线协议已经不能够满足要求了。串行总线由于更好的抗干扰性,和更少的信号线,更高的速率获得了众多设计者的青睐。而串行总线又尤以差分信号的方式为最多。而在我们的项目中的PCI- Express串行信号线正采用了LVDS技术。所以以下的叙述中都以串行信号中LVDS信号为代表讲述。

✿

串行LVDS信号的PCB设计

1. 差分信号的概念和优点

差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”,而承载差分信号的那一对走线就称为差分走线。差分信号与普通的单端信号走线相比,最明显的优势体现在以下三个方面:(1)抗干扰能力强。因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。(2)能有效抑制EMI。由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消。耦合的越紧密,互相抵消的磁力线就越多。泄露到外界的电磁能量越少。(3)时序定位精确。由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阀值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

2. LVDS信号在PCB上的设计要点

LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用,而在我们的项目中PCI-Express信号正是采用的是LVDS信号。LVDS信号不仅是差分信号,而且还是高速数字信号。因此LVDS传输媒质不管使用的是PCB线还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时应减少电磁干扰以保证信号的完整性。只要我们在布线时考虑到以上这些要素,设计高速差分线路板并不很困难。下面简要介绍LVDS信号在PCB上的设计要点:

2.1布成多层板

有LVDS信号的电路板一般都要布成多层板。由于LVDS信号属于高速信号,与其相邻的层应为地层,对LVDS信号进行屏蔽防止干扰。对于密度不是很大的板子,在物理空间条件允许的情况下,最好将LVDS信号与其它信号分别放在不同的层。例如,在四层板中,通常可以按以下进行布层:LVDS信号层、地层、电源层、其它信号层。

2.2 LVDS信号阻抗计算与控制。

LVDS信号的电压摆幅只有350mV,适于电流驱动的差分信号方式工作。为了确保信号在传输线当中传播时不受反射信号的影响,LVDS信号要求传输线阻抗受控,通常差分阻抗为100 /-10Ω。阻抗控制的好坏直接影响信号完整性及延迟。如何对其进行阻抗控制呢?(1)确定走线模式、参数及阻抗计算。LVDS分外层微带线差分模式和内层带状线差分模式。阻抗可以通过合理设置参数,利用相关软件计算得出。通过计算,阻抗值与绝缘层厚度成正比,与介电常数、导线的厚度及宽度成反比。(2) 走平行等距线及紧耦合原则。确定走线线宽及间距后,在走线时严格按照计算出的线宽和间距,两线的间距要一直保持不变,也就是要保持平行(可以放图)。同时 在计算线宽和间距时最好遵守紧耦合的原则,也就是差分对线间距小于或等于线宽。当两条差分信号线距离很近时,电流传输方向相反,其磁场相互抵消,电场相互 耦合,电磁辐射也要小得多。而且要两条线走在同一层,避免分层走线。因为在PCB板的实际加工过程中,由于层叠之间的层压对精确度大大低于同层蚀刻精度,以及层压过程中的介质流失,不能保证差分线的间距等于层间介质厚度,会造成层间差分对的差分阻抗变化。(3)走短线、直线。为确保信号的质量,LVDS差分对走线应该尽可能地短而直,减少布线中的过孔数,避免差分对布线太长,出现太多的拐弯,拐弯处尽量用45°或弧线,避免90°拐弯。

2.3不同差分线对间处理

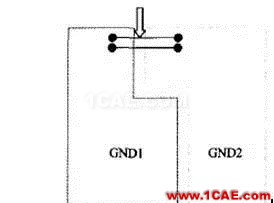

LVDS对走线方式的选择没有限制,微带线和和带状线均可,但是必须注意要有良好的参考平面。对不同差分线之间的间距要求间隔不能太小,至少应大于3-5倍差分线间距。必要时在不同差分线对之间加地孔隔离以防止相互间的串扰。LVDS信号尽量远离其它信号。LVDS差分信号不可以跨平面分割。尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续(如图所示,其中GND1、GND2为LVDS相邻的地平面)。

图1:差分对线

接收端的匹配电阻的布局。对接收端的匹配电阻到接收管脚的距离要尽量靠近。同时匹配电阻的精度要控制。对于点到点的拓扑,走线的阻抗通常控制在100Ω,但匹配电阻可以根据实际的情况进行调整。电阻的精确度最好是1%-2%。因为根据经验,10%的阻抗不匹配就会产生5%的反射。

✿

串行LVDS信号的仿真分析

以上分析了LVDS信号设计时必须注意的事项,虽然在PCB设计的时候一般都会遵守以上的规则进行,但是为了能够提高设计的正确性和准确行必须对PCB进行信号完整行仿真,通过仿真得到信号的串扰、延时、反射和眼图波形,从而达到设计即正确的目标。信 号完整性问题的仿真流程是先建立元器件的仿真模型,然后进行前仿真确定布线过程的参数和约束条件,物理实现阶段按照约束条件进行设计,最后进行后仿真,验 证设计是否满足设计要求。在整个流程中模型的精确性直接影响仿真的结果,而在前仿真和后仿真阶段用到的仿真分析方法对于仿真结果同样至关重要,而在本设计 中采用了精确度较高的spice模型。下面结合实际的项目来说明仿真在本设计的实施过程。

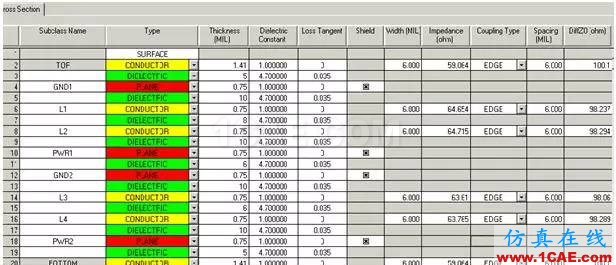

3.1. PCB叠层设置

由上面的分析知道,PCB板的叠层设置和信号的耦合以及阻抗计算都有着密切的关系,所以在开始PCB设计之前必须进行叠层设计,然后进行信号的阻抗计算。在本设计中的叠层设计见下图:

图2:叠层设计

由于PCB密度较高,本设计采用10层板的叠层结构,经过合理的安排叠层厚度,通过allegro计算,表面微带和内层带状线的差分线在线宽6㏕线间距6㏕时,阻抗理论计算值分别为100.1和98.8Ω。符合阻抗控制要求。

3.2. 设置直流电压值

这一步骤主要是为某些特定的网络(一般是电源地等)指定其直流电压值,确定DC电压加在网络上,执行EMI仿真需要确定一个或多个电压源管脚,这些电压值包涵了模型在仿真过程中使用的参考电压信息。

3.3. 器件设置

在allegro仿真的时候allegro会把器件分成三大类:IC、连接器和分立器件(电阻电容等),allegro会依据器件类型来给器件的管脚分配仿真属性,分立器件和连接器的管脚属性为UPSPEC,而IC的管脚属性可以为IN、OUT和BI等。

3.4. 模型分配

在板级高速PCB仿真过程中主要用要的模型有器件模型和传输线模型。器件模型一般是由器件生产厂家提供的。在高速串行信号中,我们采用的是精度更高的SPICE模型来进行仿真分析。传输线模型则是通过仿真软件建模形成的。信号在传输时,传输线会使得信号完整性问题突出,因此仿真软件对传输线精确建模的能力直接影响仿真结果。

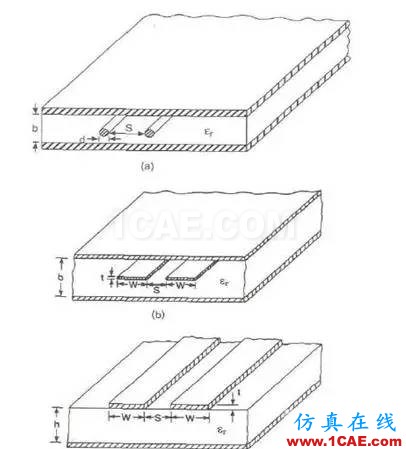

图3:差分对线模型b:带状线 c: 微带线

而 信号路径和返回路径所在的传输线不可能是理想的导体,因此它们都有有限的电阻,电阻的大小由传输线的长度和横截面积决定。任何传输线都可以划分为一系列串 接线段。同样的在传输线之间的介质也不可能是理想的绝缘体,漏电流总是存在的。实际的传输线模型由无数个短线段组成,短线段的长度趋于零。 关于传输线的模型是allegro自动分配的。仿真的时候主要是分配器件模型。

3.5. SI检查

SI Audit功能是用来检查某一个特殊的网络或者一群网络是否能够被提取出来进行分析,一般就是设置我们需要关注的高速网络,本设计主要关注LVDS串行信号。

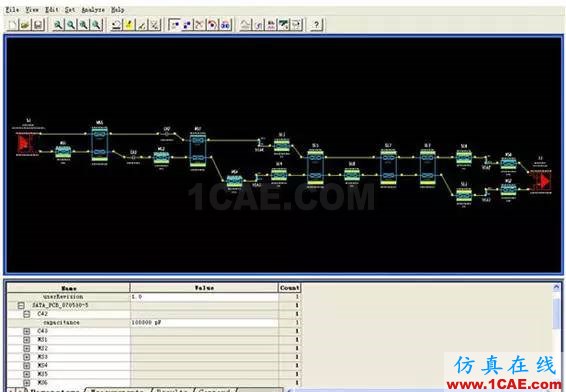

3.6.提取网络拓扑

从PCB中提取待关注信号的拓扑结构,一般包括驱动端和接收端,以及传输线和相关的匹配电阻电容等,可以从拓扑结构中看出该网络经过那些路径,那些会对信号的传输造成影响。本文仅以其中一个信号的网络拓扑图为例,如图4所示:

图:4 差分对线的网络拓扑

3.7. 查看波形

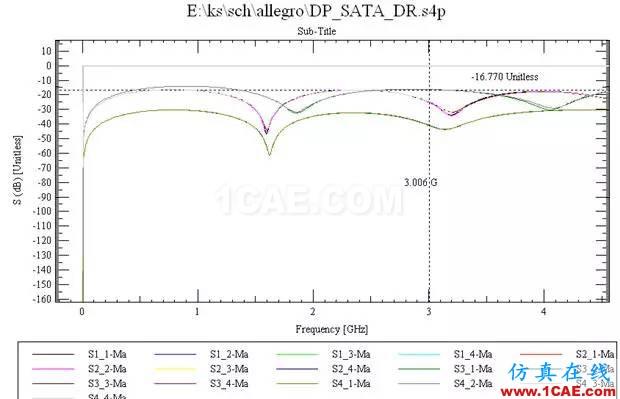

以上的相关步骤设置好以后就可以进行仿真了,allegro可以进行信号的反射仿真、串扰仿真,差分线还要进行眼图分析。当然仿真也分前仿真和后仿真,在利用allegro进行PCB设计的时候还需要结合仿真的结果实时的对设计进行修改以达到符合要求的目的。由于仿真过程复杂,步骤繁琐,在此不一一进行描述, 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,等长是为了保证两个差分信号时刻保持相反极性,减少共模分量。另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者side-by-side 实现的方式较多。等距则主要是为了保证两者差分阻抗一致,减少反射。对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。从仿真的S参数曲线图可以分析差分对的差分阻抗(differential impedance),以及信号完整性。下面给出本设计中的关键信号仿真波形以供加以说明。 从仿真图例图5看到,S11在0-3.0GHz 的频域范围内其最劣化的指标为:-16.770db以下 ,S22(粉红色的曲线)也不劣于-17db。 这说明该差分对的差分阻抗(differential impedance)接近设计指标,信号完整性得到了保证。

图5:差分对线仿真S参数曲线

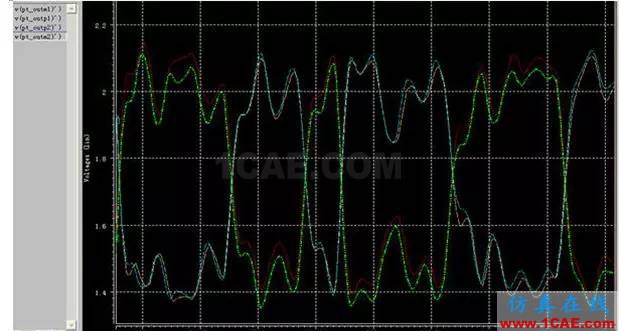

图6:差分对IN,OUT的HSPICE仿真图

通过差分对IN,OUT的HSPICE仿真,图6显示的结果:差分对线的对称良好。

结论 通过以上的仿真分析可知,在PCB的设计阶段对于高速LVDS信号的各项要求都能达到,而经过实际的PCB生产也证明了该设计的正确性,该产品运行稳定,完全能达到PCI-express高速数据传输的要求,可靠性高。由 本文的分析可知,在高速串行信号的设计中,不仅考虑电路设计,其板图设计和仿真分析也同样的重要,而且随着信号的频率越来越大,影响信号的延时、串扰、信 号完整性等的因素越来越复杂。同时控制这些因素的影响也越来越困难,工程师必须深入的分析布线设计、借助精确的模型、有效的仿真和科学的分析方法,才能给 复杂的高速设计以正确的指导,减少修正周期确保设计成功

相关标签搜索:高速串行差分信号的PCB设计与仿真 ansysem电磁培训班 ansys SIwave培训课程 ansys maxwell hfss培训和分析 ansysem在线视频教程 pcb 封装分析仿真 Fluent、CFX流体分析 HFSS电磁分析 Ansys培训 Abaqus培训 Autoform培训 有限元培训