【有源SI】DFE(Decision Feedback Equalization,判决反馈均衡)【转发】

2017-06-30 by:CAE仿真在线 来源:互联网

在没有系统的说SerDes的处理串行信号的方法,真的不该说DFE(Decision Feedback Equalization,判决反馈均衡)。但是看到这个时候,被惊艳到了,忍不住!

为什么要用DFE?

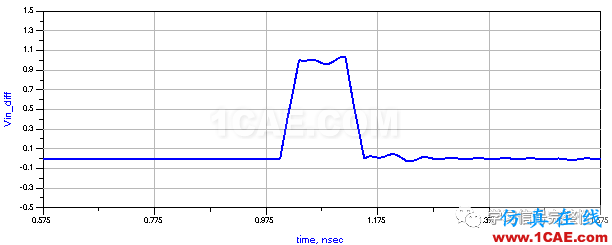

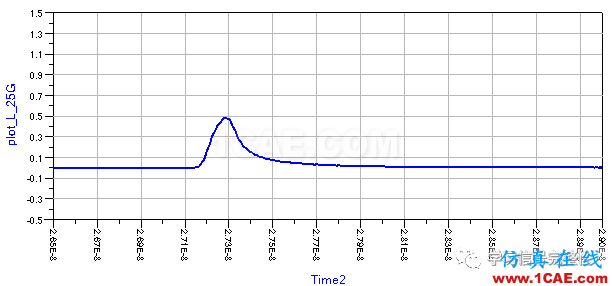

第一,我们都知道无源通道对高频信号衰减很大,导致经过通道的脉冲响应产生拖尾,这会导致ISI(Inter Symbol Interference,码间干扰)的问题。衰减越大,拖尾越长。图1的脉冲信号经过5M 26AWG DAC后输出的脉冲信号(图2),尾巴好长啊!导致隔壁的bit的电平不是0!

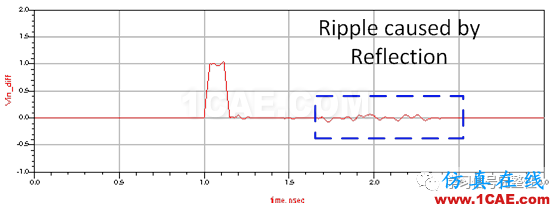

第二,无源通道里面有连接器,过孔,fan-out等,这些阻抗不连续点,会导致如图3所示的ripple,也会引起误判。

图1

图2

图3

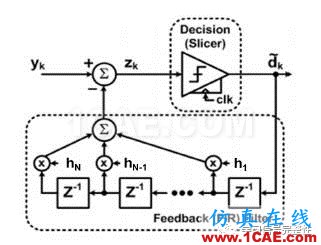

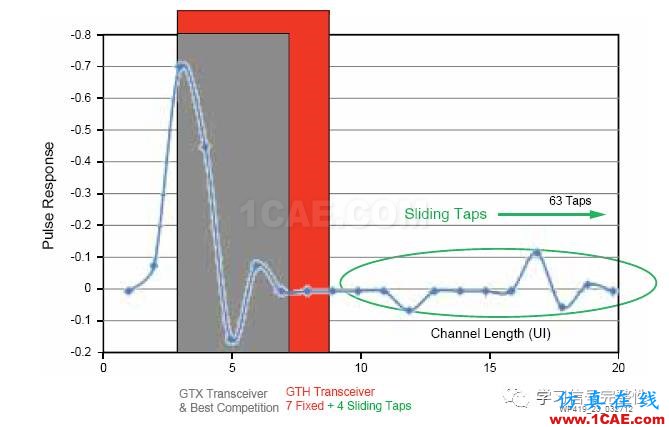

DFE的原理如图4所示,在到判决门限前,DFE将前面bit的后面的尾巴直接减掉,h1到hn是系数,软件会根据无源通道特性,自适应系数,找到最佳。需要减掉的尾巴越长,那么DFE的设计更复杂,而且功耗更高。Xilinx的GTH transciver有固定7阶,那么就是脉冲响应后面7个bit的拖尾可以被减掉。

图4

假设经过无源通道的后的脉冲如图5所示,既有ISI引起的拖尾,又有反射引起的ripple。但是因为阻抗不连续点的距离不同,ripple的位置有长有短,这个怎么办?

Xilinx的GTH transceiver有固定的7阶和可以移动的4阶,可以移动最大到63阶的位置,如图6所示,是不是被惊艳到了。这样以来,固定的7阶可以消除ISI,而移动的4阶可以把连接器的短距离的反射消除,如果是背板的应用,长距离反射也可以消除,感觉帅呆了。那么这款transceiver岂不是兼容程度很高!

图5

图6

参考文献:

Equalization for High-Speed SerialInterfaces in Xilinx 7 Series FPGATransceivers, White Paper

DesingCon2016, PAM4 signaling for 56G serial link applicaitons,Geoff zhang

转自微信公众号:学习信号完整性

相关标签搜索:【有源SI】DFE(Decision Feedback Equalization,判决反馈均衡)【转发】 ansysem电磁培训班 ansys SIwave培训课程 ansys maxwell hfss培训和分析 ansysem在线视频教程 pcb 封装分析仿真 Fluent、CFX流体分析 HFSS电磁分析 Ansys培训 Abaqus培训 Autoform培训 有限元培训