SI-list【中国】详解电源完整性(一) ▏芯片电流是随时间变化而变化【转发】

2017-06-30 by:CAE仿真在线 来源:互联网

作者陈永真,现在就职于外资芯片公司,从事芯片的电源完整和信号完整性性方面的工作,对电源完整性和信号完整性有一定的认识,借助SI-List【中国】平台,与大家分享一些对信号完整性和电源完整性方面的心得,与大家一起学习讨论,本次内容共分N期,详细介绍电源完整性的来龙去脉,在这里分享出来,主要是方便大家交流学习,如果有侵犯到您的版权,请与群主联系,及时删改,谢谢!

电源分布网络从字面上就很好理解,就是电流从供电端到用电端的一些路径网络。一个芯片需要工作,就需要有电源来提供电流。而电源与用电电路之间就必然存在电源的传输网络。就像供电站需要通过电线将电能传输到各家各户一样。

既然存在传输,就存在传输损耗。根据欧姆定律我们知道当电流流过导体,在导体两端就会产生压降。所以当电流流经电源传输网络,就会在供电端与用电端产生压降。比如需要使用10A的电流,电源传输网络的阻抗为1毫欧,那么供电端与用电端的压降就为10mV。这个问题看起来很简单,但是我们需要面对2个不简单的事情。1是用电端的电流需要是随着时间变化的,2是电源传输网络的阻抗也不是一个常数,由于趋肤效应,寄生电感,寄生电容等因素使得电源传输网络对不要频率的信号显示出不同的阻抗。

电流需要是随时间变化而变化的

要解释问题,我们有必要先了解一些数字电路的基本知识(这里我们只对CMOS数字电路进行分析,其它电路也有类似的问题)。

MOSFET场效应管

在了解数字电路前,有必要先了解一下数字电路的基本组长单元:MOSFET场效应管。MOSFET的全称是The metal-oxide-semiconductor field-effect transistor,即金属-氧化层半导体场效应管。它对于数字电路来说,主要起了一个开关的作用。它主要的优势是生产工艺很简单,使得我们可以以很经济的方式生产大规模的复杂电路。

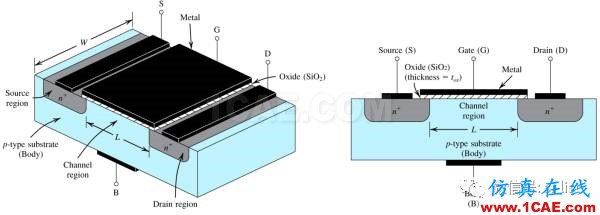

一个NMOS的基本结构下图所示,场效应管MOSFET是一个四端口器件,包括一个p型的衬底,以及两个n+型扩散区域源极source(S)和漏极drain(D),另外在源极与漏极之间的衬底表明覆盖一层薄氧化层,在该薄氧化层上沉淀形成的栅极gate(G)。

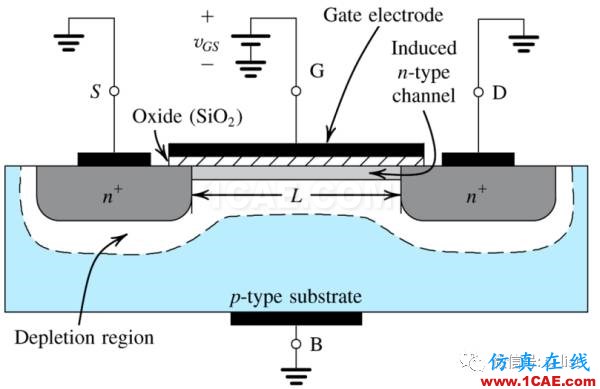

NMOS管的工作原理是,栅极与p型衬底由薄的氧化层隔开,从而形成一个电容。而源极,p型衬底以及漏极则由2个pn(S-B以及D-B)结形成背对背的二极管,从而源极与漏极之间实现了绝缘。当有一个比较小的正电压施加到栅极时,电子开始向栅极方向累积,同时电场作用下,空穴开始朝衬底方向移动。当栅极电压超过一定的电压阈值Vt之后,便在衬底表面形成一个由大量电子组成的n型的导电沟道,如下图所示:

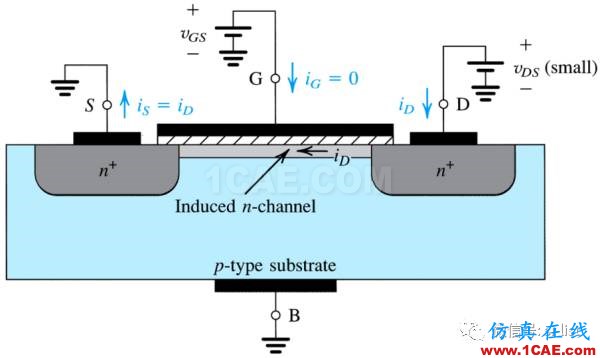

在导电沟道形成以后,一旦有电压施加到漏极与源极之间,电子通过导电沟道进行运动,就在源极与漏极之间形成了电流的流动,如下图所示。

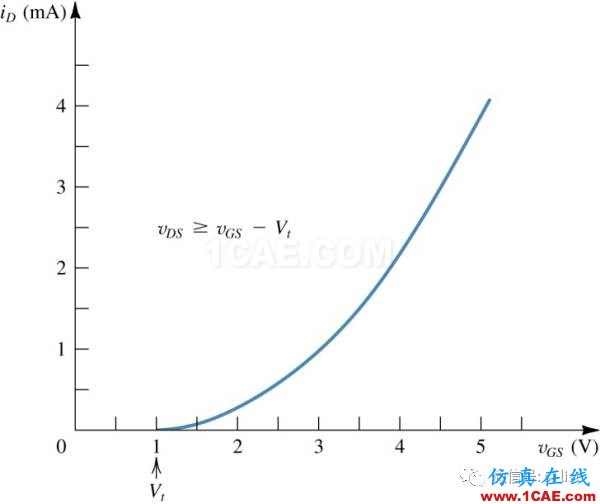

如下图所示,随着V_{GS}的增大,沟道开始逐步形成,当V_{GS}大于某个阈值电压V_{t}以后,沟道连通源极与漏极,开始有电流从源极流向漏极,随着V_{GS}的持续增加,电流也不断增加。

PMOS与NMOS恰巧相反,采用n型衬底,源极及漏极为p+型扩散区。也就是说在V_{GS}为0时,源极与漏极之间存在导电沟道,随着V_{GS}增加,导电沟道会变窄,最终当V_{GS}大于某个阈值电压V_{t}时,沟道正式关闭。

CMOS反相器

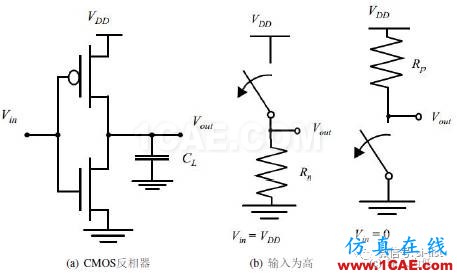

如果单独使用NMOS或者PMOS,电路存在比较大的静态电流。于是出现了CMOS电路。如下图a所示就是一个CMOS的示意图。是由一个PMOS场效应管的漏极与一个NMOS场效应管的源极连接在一起组成。

我们知道,对于NMOS管来说,关断电阻为无穷大,导通电阻比较小。这样当V_in为高电平或者等于VDD的时候,NMOS就被导通,同时PMOS关断。这时的等效电路如上图b。输出V_out和ground结点之间有一个直接的通道,导致输出处于一个稳定的0V。当输入为低电平(0V),NMOS关断,PMOS导通,等效电路如上图c,这时输出V_out与V_DD之间存在一个直接通道,所以输出为高。最终电路表现出一个反相器的功能。

我们可以通过这个交换器模型看到静态CMOS电路具有如下属性:

-

高电平为VDD,低电平为GND,也就是说电压的摆幅等于电源电压,这样就会有比较大的噪声容限;

-

逻辑电平与器件的面积没有关系,这样场效应晶体管可以尽可能的使用比较小的面积。

-

在稳定状态下,输出$V_{out}$与电源$V_{DD}$或者GND之间存在一个有限阻抗的直流通道。通常情况下,一个良好设计的CMOS反相器,输出阻抗都会比较低。

-

CMOS反相器的输入阻抗一般情况下都非常高,也相当于绝缘,几乎没有什么直流电流消耗。因为输入时连接到晶体管的栅极,静态情况下,输出电流几乎为0.这样,理想情况下,一个反相器可以驱动无数个栅极(也就是说可以有无限的扇出),同时还能保证功能正常。当然,输出扇出增加也会增加延迟,影响晶体管的响应特性。

-

在稳态状况下,电源和地之间不存在通路,这也导致在稳态情况下,几乎没有电流的流动,晶体管也就没有任何的静态功耗。

CMOS电路的动态特性

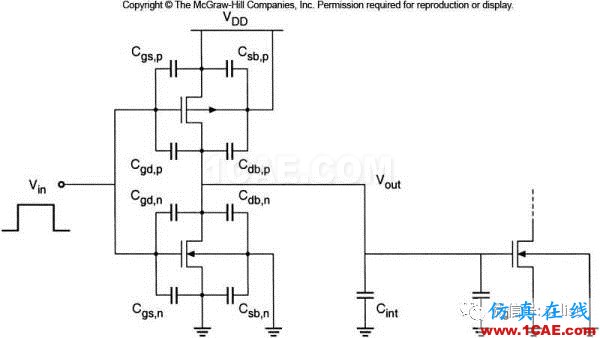

前面分析了稳态是CMOS电流的一些特性,那么我们看看当CMOS电路运行的时候,流经CMOS器件的电流情况。分析CMOS电路的动态特性时,我们就必须考虑CMOS器件的继承电容。如图所示,显示了两个CMOS反相器的级联,每一个MOSFET均有寄生电容, 包括:

C_{gd}和C_{gs}: 由栅极和源极与漏极重叠产生的栅源电容以及栅漏电容。

C_{db}和C_{sb}: 漏极与衬底和源极与衬底之间形成的与电压有关的结电容。

C_g: 由栅极下面的薄氧化而形成的栅电容。

C_int: 两个CMOS反相器之间连线的寄生电容。

即使是对于这个很简单的电路来说,分析这个输出波形也是相当的复杂,因为这里面有很多非线性的电压相关的电容。为了简化问题,我们将s图中的电容转化为一个集总的线性电容,连接到输出结点和地之间,如下图所示:

其中C_{load}定义如下:

Cload = C(gd,n) + C(gd,p) + C(db,n) + C(db,p) + Cint + Cg

注意: 有一些寄生电容没有包含在上图中,因为两个CMOS反相器的源-衬底的电压始终为0, 电容C_{sb,n}和C_{sb.p}也为0.电容C_{gs.n}和C_{gs.p}因为连见到输出结点和地(电源)之间,而没有包含进来。

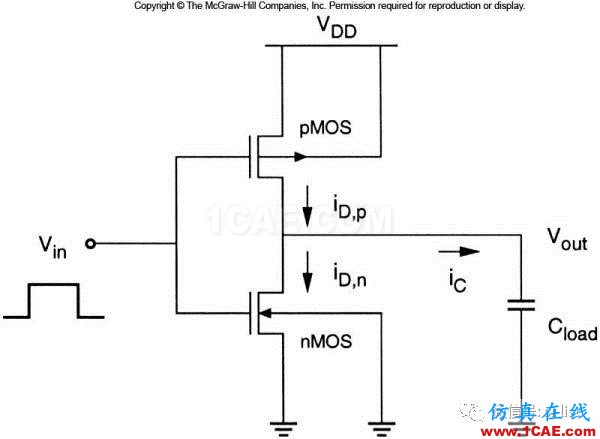

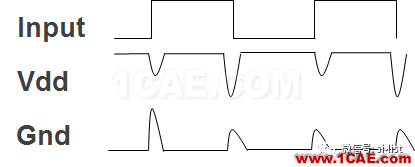

使用上图,使得问题简化为分析一个CMOS反相器对一个电容进行充电和放电的动作。当输出为0时,PMOS打开,NMOS关闭。电源通过PMOS对输出电容进行充电,最终达到稳态。负载电容两端电压等于电源电压V_{DD}。当输入电压提升,PMOS的沟道减小,但是PMOS的漏极与源极电压均为V_{DD},没有电流流过PMOS管。假设NMOS和PMOS的阈值电压V_{t}均为1/2(V_{DD}),当输入电压达到1/2(V_{DD}),NMOS打开,同时PMOS关闭。负载电容通过NMOS对地放电。此时会有电流流过地平面,使得芯片内地平面抬升。

同时我们分析当输入信号由高电平转换到低电平时的情况。当输入为高电平,NMOS管打开,PMOS管关闭,输出为低。输入电压持续降低,当输入电压低于1/2(V_{DD}),PMOS打开,NMOS关闭。V_{DD}开始通过PMOS对输出负载电容进行充电。此时有电流从电源流进用电芯片。下图显示了CMOS电路在动态情况下电压变化情况。

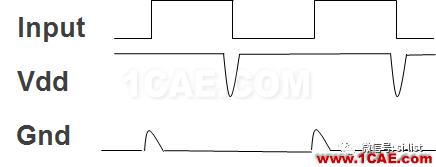

而实际的情况比上图显示的还要糟糕。因为导电沟道的变化是一个连续的渐进过程,NMOS和PMOS并不是理想开关,在实际过程中会存在阶段,PMOS和NMOS同时打开,这是V_{DD}与GND之间形成一个直接的导电通道。好的一点时,此时NMOS与PMOS的导电沟道宽度都很小,使得此时的电流并不是无限大。一个实际CMOS电路的电压图如下图所示。

所以我们可以看到CMOS电路消耗的电流是随着时间的变化而变化的。

转自微信公众号:SI-list【中国】

相关标签搜索:SI-list【中国】详解电源完整性(一) ▏芯片电流是随时间变化而变化【转发】 ansysem电磁培训班 ansys SIwave培训课程 ansys maxwell hfss培训和分析 ansysem在线视频教程 pcb 封装分析仿真 Fluent、CFX流体分析 HFSS电磁分析 Ansys培训 Abaqus培训 Autoform培训 有限元培训

NMOS管的工作原理是,栅极与p型衬底由薄的氧化层隔开,从而形成一个电容。而源极,p型衬底以及漏极则由2个pn(S-B以及D-B)结形成背对背的二极管,从而源极与漏极之间实现了绝缘。当有一个比较小的正电压施加到栅极时,电子开始向栅极方向累积,同时电场作用下,空穴开始朝衬底方向移动。当栅极电压超过一定的电压阈值Vt之后,便在衬底表面形成一个由大量电子组成的n型的导电沟道,如下图所示:

NMOS管的工作原理是,栅极与p型衬底由薄的氧化层隔开,从而形成一个电容。而源极,p型衬底以及漏极则由2个pn(S-B以及D-B)结形成背对背的二极管,从而源极与漏极之间实现了绝缘。当有一个比较小的正电压施加到栅极时,电子开始向栅极方向累积,同时电场作用下,空穴开始朝衬底方向移动。当栅极电压超过一定的电压阈值Vt之后,便在衬底表面形成一个由大量电子组成的n型的导电沟道,如下图所示:

在导电沟道形成以后,一旦有电压施加到漏极与源极之间,电子通过导电沟道进行运动,就在源极与漏极之间形成了电流的流动,如下图所示。

在导电沟道形成以后,一旦有电压施加到漏极与源极之间,电子通过导电沟道进行运动,就在源极与漏极之间形成了电流的流动,如下图所示。

PMOS与NMOS恰巧相反,采用n型衬底,源极及漏极为p+型扩散区。也就是说在V_{GS}为0时,源极与漏极之间存在导电沟道,随着V_{GS}增加,导电沟道会变窄,最终当V_{GS}大于某个阈值电压V_{t}时,沟道正式关闭。

PMOS与NMOS恰巧相反,采用n型衬底,源极及漏极为p+型扩散区。也就是说在V_{GS}为0时,源极与漏极之间存在导电沟道,随着V_{GS}增加,导电沟道会变窄,最终当V_{GS}大于某个阈值电压V_{t}时,沟道正式关闭。