【无源SI】Skew【转发】

2017-06-30 by:CAE仿真在线 来源:互联网

高速PCB走线,发现转角的地方都有很多补偿走线凸包;

很多PCB layout guideline里面,都强调要走45度角,而且走一段后,再反转走线;

测试25G信号眼图的时候,需要差分对的两根同轴相位控制到10%以内,如果更高速率,要求更高。

Why? Why? Why?

因为这些都是在减小skew。

第一个减小走线长度不对等引起skew;

第二个减小PCB玻璃纤维的引起skew;

第三个减小RF cable的不对称引起skew;

第一,Skew的定义

|

名称 |

介绍 |

带来什么问题 |

什么原因 |

图例 |

|

Intra-pair skew |

差分对两根线,N和P之间延时差;一般在ps量级; |

导致jitter,EMI,串扰等 |

长度不一样;差分对介质不均匀等; |

图1 |

|

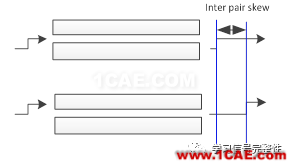

Inter-pair skew |

差分对之间的延时差;一般在ns级; |

会影响接受信号的不同通道对齐处理,长延时对接收端的buffer要求高。 |

图2 |

因为intra pair skew会引起信号质量问题,所以最长关注就是intra pair skew的影响。

图1

图2

第二,skew的测试

Inter pair skew就是测试不同差分对的delay,delay差就是skew了。

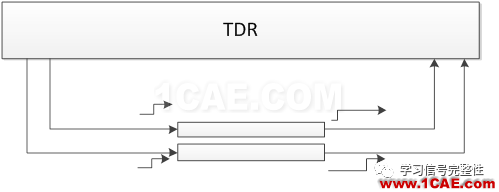

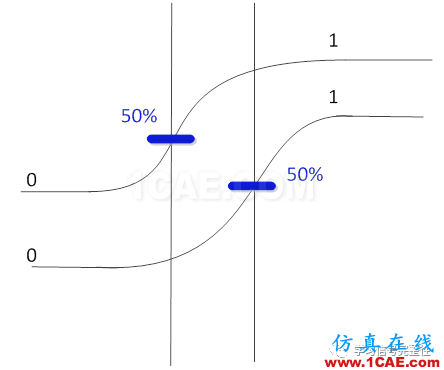

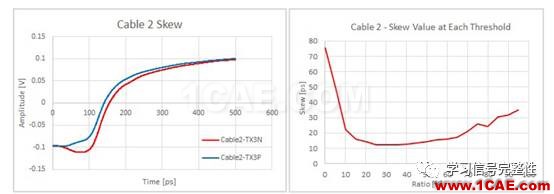

我们主要讨论intra pair skew,常用的测试方法就是TDT模式,测试如图3所示。理想当然是阶跃信号,但是实际上传输到TDT的接收的时候,已经变得很缓慢,如图4所示。

这个时候就涉及到一个参考电平取得问题。如图5所示,不同参考电平的百分比下,测试出来的差异从10ps到75ps。但是在20%到60%之间比较稳定,差异在5ps左右。但是对于时域测试来说,采用这个位置的参考点已经是比较准确的位置了。

图3

图4

图5

第三,Skew在频域的标准

to be continued!

参考文献:

Design Con 2017,mathematically de-mystifying skew impacts on 50G SerDes links, Hansel Dsilva ect

转自微信公众号:学习信号完整性

相关标签搜索:【无源SI】Skew【转发】 ansysem电磁培训班 ansys SIwave培训课程 ansys maxwell hfss培训和分析 ansysem在线视频教程 pcb 封装分析仿真 Fluent、CFX流体分析 HFSS电磁分析 Ansys培训 Abaqus培训 Autoform培训 有限元培训