超导RSFQ计算机

2017-02-14 by:CAE仿真在线 来源:互联网

来源:《中国计算机学会通讯》2016年第3期《专栏》

作者:唐光明

引言

2015年,国产超级计算机“天河二号”以理论峰值计算速度54902.4TFlop/s、实际峰值运算速度33862.7TFlop/s第六次蝉联世界超级计算机500强第一名,当之无愧成为全球最快的超级计算机。它是由312万个计算核心构成,功耗为17808.00 kW,峰值运算时能耗比为1.9GFlops/W。2015年,最省电的超级计算机是日本理化所信息中心的菖蒲(Shobu)集群,其能耗比为7.03GFlops/W。我们如果利用现在的半导体集成电路技术,即使在不断改进计算机系统结构和制造工艺技术的情况下,要想制造出满足“大数据”时代需要的能耗比为50 GFlops/W的E级计算机也将十分困难。其中面临的最大挑战就是难以忍受的巨额耗电量和由此带来的散热问题。因此,各国研究者们都在开始寻找可替代半导体的新器件。

2015年,是超导现象被发现104周年和约瑟夫森效应被发现53周年。超导高速单磁通量子(Rapid Single-Flux-Quantum, RSFQ)电路因其具有超高运算速度和超低功耗的特性而受到研究者们关注。客观地讲,因超导自身特性,使其应用局限于只追求超高运算速度和超低功耗的特殊应用领域。因为难以实现大容量存储器和单位面积上约瑟夫森结较高集成密度,致使该技术永远不可能成为主流数字集成电路技术。虽然一直有工业界的参与和政府的大力支持,但是至今为止仍没能制造出一台完整的超导计算机。

在本文中,我们首先介绍RSFQ数字电路的基本特征、意义和应用前景,然后了解以前几个超导计算机项目及研究现状,最后展望超导RSFQ计算机未来的发展方向及其面临的挑战。

超导RSFQ电路技术及其EDA工具

超导RSFQ电路中的基本构成器件为约瑟夫森结(Josephson Junction, JJ),通过在两个超导体之间加一层厚度约为2~3nm的绝缘层形成。由于隧道效应,会有约瑟夫森电流经过两个超导体。约瑟夫森结可以由电流控制工作状态,能够在几个皮秒内改变状态并产生一个单磁通量子(Single-Flux-Quantum, SFQ)脉冲。在RSFQ数字电路中,使用的是脉冲逻辑(pulse logic):出现SFQ脉冲时代表逻辑值“1”,否则为逻辑值“0”。表1比较了日本不同超导RSFQ数字集成电路制造工艺的性能。从中可以看出,超导芯片能够达到传统CMOS工艺无法达到的工作频率。

与半导体芯片设计方法类似,设计超导芯片时必须要使用集成电路设计软件。2006~2012年,日本名古屋大学计算机系高木直史教授(2010年调入京都大学计算机系)主持的“高性能低功耗单磁通量子处理器”项目中,研究人员使用SKILL语言编程调用Cadence提供的各种接口实现了超导RSFQ大规模集成电路设计的电子自动化。与CMOS芯片设计不同,在RSFQ芯片设计中,根据不同的时钟供给方式,需要准确计算每个数据和时钟到达每个逻辑门的时间,并使其满足每个逻辑门的保持时间和建立时间要求,以此保证每个逻辑门能正常工作。但在大规模RSFQ数字集成电路设计中,计算这两个时间需要花费大量时间。为了缩短设计周期,高木研究室的研究人员设计了自动计算这两个时间的工具箱,这大大缩短了现在日本的RSFQ大规模集成电路设计周期。

2002年国际超导产业技术研究所超导工学研究所(SRL)、情报通信研究机构(NICT)(神户)、名古屋大学和横滨国立大学共同开发了适用于工艺STP2的CONNECT单元库。该单元库包含200多个逻辑门和传输线。每个CONNECT单元都由数字层、模拟层和版图构成。每个单元的数字层用Verilog HDL虚拟硬件语言描述了单元的数字行为,主要定义在不同偏置电压条件下单元的保持时间和延迟时间等;模拟层定义单元的模拟电路模型,主要包括电感、电阻、电容、约瑟夫森结等参数,并负责从数字层提取各种时间参数以完成低频功能时序仿真;根据STP2工艺将模拟层定义的各种电路模型参数以相应厚度、长度和宽度物理实现到不同层就得到了单元的版图。后来在CONNECT单元库的基础上又开发出了适用于ADP2工艺标准的ADP单元库。这样,我们就可利用EDA工具将计算机体系结构人员设计的RSFQ逻辑电路进行布线布局形成大规模集成电路并进行设计规则检查(DRC)和电气规则检查(ERC),局部修改后通过检查就可以生成GDSII版图文件交付日本产综研(AIST)进行RSFQ芯片制造。芯片被制造完成后再送到名古屋大学藤卷研究室由田中雅光带领的小组进行高频测试。

在美国,纽约州立大学石溪分校(SBU)开发了适用于HYPRES 4.5kA/cm^2 1.5μm 4层铌工艺的单元库SBU VHDL单元库。现在还没有适用于MIT林肯实验室10层铌工艺单元库的相关报道。

超导RSFQ计算机的发展

1972~1983年,IBM首次尝试使用约瑟夫森结制造超导计算机。在这个项目中,研究人员使用铅合金制造约瑟夫森结,导致电路热周期特性不稳定;以及采用与CMOS电路类似的工作逻辑,需要另加交流电完成复位,从而使超导数字电路丧失了在速度上的优势。

继IBM项目失败15年之后,RSFQ电路理论奠基人纽约州立大学石溪分校教授利哈廖夫(K. K. Likharev)领导了混合技术多线程(HTMT)体系结构超导计算机项目(1996~2000)。当时的制造工艺仅仅只能实现几千个约瑟夫森结的集成度,无法满足HTMT中每个处理器芯片需要几百万个约瑟夫森结的要求。最后,由几万个处理器构成的HTMT超导计算机系统以没有制造出一个芯片而告终。

有了以上两个项目失败的经验教训后,美国人开始从实际出发,结合工艺水平,研制8位并行处理器FLUX-1。虽然美国人并没有打算将此处理器应用到任何地方,但最后该项目并没有成功演示一个完整的并行超导RSFQ处理器。

由于受到约瑟夫森结集成度的限制,日本主要集中研制8位串行结构处理器。但是实际应用中真正需要的是32位或64位处理器。2012年日本发展了ADP2制造工艺,可以在1cm^2的芯片上集成105个约瑟夫森结的同时并开发了超导无源传输线PTL,使32位RSFQ处理器的实现成为可能。所以,现在日本名古屋大学(负责芯片物理实现和测试)、京都大学(负责计算机体系结构和硬件算法)、横滨国立大学(负责存储器)和AIST(负责芯片制造)开始共同研制32位串-并体系结构处理器,并且已经成功演示基于4位串-并体系结构的32位ALU。该成果已经于2016年1月在IEEE Transactions on Applied Superconductivity 26卷第一期上发表。4位串-并体系结构32×32位乘法器也被设计完成,该成果将于2016年6月被发表在IEICE Transactions on Electronics E99-C卷第6期上。美国仍继续研制并行体系结构32位/64位处理器。直到2015年,只有日本成功演示了完整的8位串行处理器CORE1。

8位串行体系结构微处理器

2002~2007年,日本名古屋大学、横滨国立大学、东北大学、SRL、NICT(神户)共同开展CORE1处理器项目。虽然功能简单,但CORE1仍是至今唯一被成功演示且功能完整的处理器。

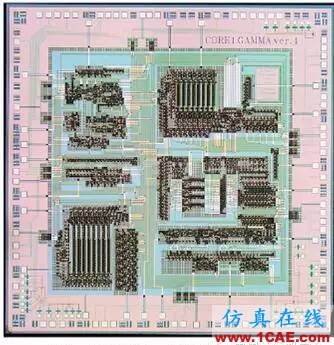

CORE1α(ver.5)是第一个被成功演示的RSFQ处理器。它包含4999个约瑟夫森结,工作时钟为15GHz,功耗为1.6mW,性能为167MIPS(每秒百万条指令)。在CORE1α(ver. 6)中使用了超导无源传输线 PTL技术,包含6319个约瑟夫森结,工作时钟为18GHz,功耗为2.1mW,性能提高到240MIPS。后来又发展出CORE1α(ver. 10),CORE1β,CORE1γ(ver.2)等几个版本,图1所示的CORE1γ(ver.4)是CORE1的最后一个版本,包含22302个约瑟夫森结,面积为6.36×6.20mm^2,性能为666 MOPS(峰值),拥有四级流水线,工作时钟频率25GHz,功耗为6.56mW。

高性能低功耗超级计算机系统结构

1997~2001年,日本科技厅确立RSFQ电路基础技术研究项目,SRL、AIST、富士通、日立、日本电气公司(NEC)、NICT、东北大学、横滨国立大学、名古屋大学等开展对相关技术的研究。2002~2006年国立研究开发法人新能源产业技术综合开发机构(New Energy and Industrial Technology Development Organization, NEDO)确立RSFQ数字电路设计技术研究项目。

从2006年秋开始,以用RSFQ电路来开发高性能低功耗计算机为目标,JST-CREST确立了“计算机系统超低功耗技术革新和融合技术”研究领域的“高性能低功耗单磁通量子处理器”项目,对相关基础技术进行深入研究。领导者为名古屋大学计算机系高木直史教授,参与研究的单位有:九州大学计算机系村上和彰研究室、名古屋大学量子工学系藤卷朗研究室、横滨国立大学吉川信行研究室、SRL日高睦夫研究小组。

该项目开始时,SRL和NEC已经拥有了成熟的2μm超导集成电路工艺,并正在此基础上进行1μm工艺的研究。在2μm工艺中,基于元件库的设计技术已经成熟,拥有了完备的基本逻辑单元库,且正在开展JTL自动布线工具的研发。虽然可以开发Nb六层的器件,但是没有任何针对1μm工艺的设计与开发环境。

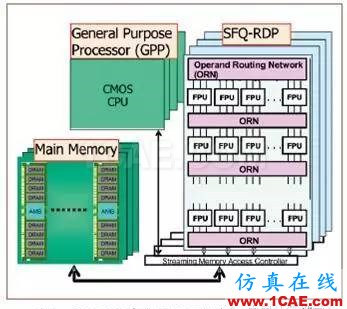

在该项目中,研究者提出可用“大规模可重构数据通路(LS-RDP)”(见图2)作为一种未来RSFQ电路实现超级计算机的体系结构。在LS-RDP中,由数千个浮单元(FPU)互联构成一个可重构的网络(Operand Routing Network, ORN),并将这种大规模具有计算机功能的加速器加入处理器中。LS-RDF具有可重构功能,大多数FPU采用并行流水线结构,具有数据依赖关系的命令均可以被直接执行。在此RSFQ电路中,只要ORN的重构被完成,LS-RDP内部的数据流向就被确定,各个FPU处理后的数据依次被传输直至运算完成,且计划用RSFQ电路实现LS-RDP中数据读取的“流缓冲”。整个项目中的处理器、主存储器等均采用半导体器件。为了在将来能完全实现超导RSFQ计算机系统,日本当前正在进行32位串-并体系结处理器的研制。

32位串-并体系结构计算机

由日本科学振兴机构(JST)战略创造研究推进事业先端低碳技术开发项目下支持的“Superconductor Electronic System Combined with Optics and Spintronics (2011~2017)”项目计划研制一个超导RSFQ计算机系统。名古屋大学藤卷朗主持此项目,参与单位有NICT、横滨国立大学、京都大学和AIST。此项目中的核心单元为一个采用MIPS32指令系统的RSFQ微处理器,由京都大学高木研究室负责此处理器的体系结构和硬件算法研制工作。该研究小组采用串-并体系结构,现在已经完成ALU和乘法器研制工作。之所以采用串-并体系结构,是因为串行结构处理32位数据速度太慢,不能采用;也不能采用并行体系结构,因为现在日本最先进的ADP2工艺只能在1cm^2芯片上集成10万个约瑟夫森结,而负责美国C3超导RSFQ计算机项目中计算机体系结构设计的SBU研究小组设计的32位并行算术逻辑单元需要36073个约瑟夫森结,32×32位并行乘法器需要75811个约瑟夫森结,这致使无法在一个芯片上实现32位处理器。因为,程序计数器(PC)、指令存储器(IM)、数据存储器(DM)和控制器(Controller)等也是处理器必不可少的部件。美国C3计划中约瑟夫森结设计复杂度为107,需要每平方厘米高达106个约瑟夫森结集成密度。但就目前HYPERS和MIT林肯实验室公开的数据来看,还没有达到这一目标。

在算术逻辑单元设计过程中,为了能发现只须消耗硬件资源较少就可达到最快速度的体系结构。我们通过一系列研究发现,即使将来约瑟夫森结的集成度增加了,也不一定会采用并行体系结构。因为,在32/64位处理器中,随着电路规模增加,单元器件增多致使时钟信号要使用大量有源分支元件Splitter,加之流水线级数加深,从而导致其处理数据的时间延迟急剧增加。所以在RSFQ数字电路中,并行体系结构并不一定有效,串-并体系结构可能是一种比较好的解决方案。

为了验证上面的结论,我们选取了硬件资源消耗较少,计算速度最快(当工作频率在35GHz以上时)的基于4位串-并体系结构的算术逻辑单元进行仿真、DRC和ERC,然后生成GDSII二进制文件送到AIST进行流片,最后到名古屋大学藤卷研究室进行高频测试。测试结果显示:该算术逻辑单元可执行MIPS32的所有算术/逻辑指令,工作频率为50GHz,功耗为1.01毫瓦,面积为3.09×1.66mm^2,消耗资源为3481个约瑟夫森结。图3(a)~(c)分别显示了封装后的芯片以及电子显微镜下芯片内部的RSFQ电路。

64位并行体系结构计算机

2005年,美国国防部情报高级研究计划署(IARPA)制定了超导RSFQ数字集成电路的发展纲要,2013~2018年开始实施Cryogenic Computing Complexity(C3)项目第一阶段的研究,主要研制超导存储器和逻辑电路关键技术,并以此寻求开发、验证超导RSFQ数字电路在超级计算领域的潜力。

该项目最终的目标是分三个阶段实现超导计算机系统。该计算机系统工作时钟频率为10GHz,吞吐量达1013bit-op/s,主存储器228字节,缓存为215字节,I/O速度为109 bit/s。处理器为64位ARM或Intel Atom核,指令集采分别用ARM或简单x86指令系统算术逻辑单元,只能处理一个64位整数,无浮点运算能力。整个逻辑电路的约瑟夫森结复杂度达107,需要流片工艺106JJs /cm^2。MIT林肯实验室负责芯片制造,他们的目标是2015年在单位面积上集成105个约瑟夫森结,到2020年约瑟夫森结集成度达106。SBU负责计算机体系结构和逻辑电路设计,目前已完成32位并行算术逻辑单元和32×32位并行乘法器的设计与仿真工作。IBM,Northrop Grumman也参与了这个项目。

未来面临的挑战

RSFQ数字集成电路虽然拥有超低功耗和超高速度的优点,但由于这是一项全新的技术,也面临许多有待解决的问题:

-

温度引起的延迟抖动:使用超导约瑟夫森结构成的RSFQ数字电路逻辑门没有固定的传输延迟,当工作环境有热波动时,RSFQ数字电路逻辑门的传输延迟随之就会产生抖动。这种现象在超高速和高宽带数据通路的处理器中尤其容易发生。因此,我们在设计RSFQ数字集成电路时,必须要提供高可靠性的时钟同步技术。

-

磁通捕获效应:当磁通被捕获或被冻结时,RSFQ数字电路的性能将被降低,从而导致操作故障。这种现象容易发生在从常态到超导态的转变过程中。为了使磁通捕获效应最小化,我们既需要采用双层金属钼(Mu)屏蔽地球磁场,也需要在超导芯片版图的接地层和面积较大的超导薄膜层上构建磁通阱(trap)或堑(moat)结构,从而使已被冻结的磁通远离正处于工作状态的RSFQ数字电路。

-

难以接受的延迟开销:在RSFQ大规模数字集成电路中,较大规模的扇出(fan-out)会造成较大的延迟开销。尤其是使用了“准备好”信号的异步并行流水线结构中, 由于逻辑门数量增大,延迟开销就会被相应增加。因为在这类电路中,需要大量使用将信号一分为二的有源分支元件Splitter,这使我们必须要额外增加大量约瑟夫森传输线JTL将这些Splitter级联起来,从而导致整个电路的延迟开销被大大增加。因此,我们在设计RSFQ大规模数字集成电路时,体系结构和逻辑电路设计阶段的工作尤为重要,需要不断优化设计,最大限度地减少电路的扇出规模,从而使整个电路的延迟开销最小化。

-

静态功耗:在RSFQ数字电路中,偏置电阻的静态功耗最大。这在RSFQ大规模数字集成电路中是一个不容忽视的问题。目前,美国HYPRES的奥列格·穆汉诺夫(Oleg A. Mukhanov)正在开展对能量有效RSFQ(Energy-Efficient RSFQ)数字电路的研究,以期待解决RSFQ数字电路中静态功耗的问题。

-

RSFQ超大规模数字集成电路EDA工具:我们虽然可以利用JSim(免费约瑟夫森结电路仿真器)、PSCAN’96(约瑟夫森结电路仿真器)、SPICE3(约瑟夫森结电路仿真器)、WRspice(约瑟夫森结电路仿真器)、InductEx(免费3D电感修改器)、SONNE(3D电磁仿真器)、HFSS(3D电磁仿真器)、LASI(免费IC版图工具)等工具来仿真和评估RSFQ数字电路,但是这些工具无法完成LSI和VLSI级RSFQ数字电路的仿真和评估。本文中提到的EDA软件要求体系结构和硬件算法设计人员完成后端设计,这就增加了设计周期。2009年,由南非开发的商业EDA软件NioCAD是一款类似Cadence的集成开发环境,不过它现在仍处于发展阶段,仍有待继续完善其功能。

-

存储器:RSFQ数字电路领域面临的最大挑战可能就是存储器。因为存储器的性能直接制约整个处理器以及整个计算机系统的性能,为此需要提供低延时、高吞吐量寻址能力的片内和片外存储器。目前,研究者们正在研究约瑟夫森磁阻随机存取存储器(Josephson Magnetoresistive Random-Access Memory, JMRAM)和重新出现涡旋转换存储器(re-emergence of vortex transition memory)。在没有出现高性能的超导存储器之前,日本研究者使用数据延迟单元DFF(Data/Delay Flip-Flop)来作为片内存储器。其优点是实现容易,但其缺点是占用面积大,消耗硬件资源多。为了验证程序计数器、控制器和存储器等部件的功能,以便在以后要设计的32位串-并处理器中应用,在近期设计的8位增强版CORE e4中增加了32个8位数据存储器和32个8位指令存储器,它们占用的面积和约瑟夫森结数量几乎占了整个芯片的50%。

总结

较目前的半导体CMOS数字集成电路,超导RSFQ数字集成电路在功耗和速度两方面都有绝对优势。但是受超导自身性能影响,其工作环境要求在零下270摄氏度(~4.2K),而且还要增加双层金属钼屏蔽地球磁场。这就意味着用超导RSFQ数字集成电路制成的设备还需要附加冷冻和屏蔽装置。因此,此技术不能应用于便携式设备和手持嵌入式设备中;更由于超导存储器和约瑟夫森结高集成度难以实现,所以RSFQ电路技术不能替代CMOS电路技术而成为主流数字集成电路技术,仅局限于只追求超高速运算速度和超低功耗而可以忽略其缺点的应用。

从科学技术发展的历史长河来看,虽然超导RSFQ数字集成电路还存在许多需要解决的问题,但对需要超高速运算速度和超低功耗的应用仍具有吸引力。

致谢:

作者衷心感谢中科院计算所黄博文工程师的编辑工作,帮助作者将近60页的原始文档缩减到仅为18页的文稿。感谢中国科学院计算技术研究所所长孙凝晖研究员和先进计算机系统研究中心副主任包云岗研究员给予的支持。正因为有了他们的帮助,本文才能与大家见面。作者的研究得到了ALCA-JST资助,CRAVITY制造了作者设计的芯片,京都大学高木研究室和名古屋大学藤卷研究室为作者开展工作提供了良好的条件,在此也一并表示感谢。

作者:

唐光明

日本京都大学,工学博士。主要研究方向为计算机体系结构、大规模单磁通量子集成电路设计。

相关标签搜索:超导RSFQ计算机 机械设计培训课程 基于数字方式的制造业升级 工业4.0 中国制造2025 CAD CAM自动化智能化机械制造的应用 Fluent、CFX流体分析 HFSS电磁分析 Ansys培训 Abaqus培训 Autoform培训 有限元培训